## SHARP ELECTRONICS (UK) LIMITED

# CA1/CA10 Chassis Course Notes

## Contents

| Introduction to the CA10 Chassis                                                         | Page 1                                                                                                                    |

|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| CA10 Receiver Specifications                                                             | Page 2                                                                                                                    |

| CA10 Block Diagram                                                                       | Page 3                                                                                                                    |

| Snubber circuit    I      Power on control    I      Primary processor power supply    I | Page 4<br>Page 5<br>Page 5<br>Page 8<br>Page 8<br>Page 9<br>Page 9<br>Page 10<br>Page 10<br>Page 11<br>Page 11<br>Page 11 |

| Primary Processor                                                                        | U                                                                                                                         |

| Resets and oscillators    I      Data communication    I      I <sup>2</sup> C bus    I  | Page 14<br>Page 14<br>Page 14<br>Page 15                                                                                  |

| Line time base generation                                                                | Page 21<br>Page 24<br>Page 25<br>Page 25                                                                                  |

| Vertical time base generation                                                            | Page 27<br>Page 27<br>Page 29                                                                                             |

| Tuner and IF Tuner and IF processing                                  |                    |

|-----------------------------------------------------------------------|--------------------|

|                                                                       | -                  |

| Tuning features                                                       | Page 32            |

| IF signals                                                            |                    |

| Audio IF processing                                                   | Page 34<br>Page 34 |

| RF AGC operation                                                      | Page 35            |

|                                                                       | Page 35            |

| Audio Processing                                                      | Page 36            |

| Signal sources and generation                                         |                    |

| Signal switching                                                      | -                  |

| Loudspeakers driver stage                                             |                    |

| Sound Retrieval System (SRS)                                          |                    |

|                                                                       | r age oo           |

| Video Processing                                                      |                    |

| Signal sources and switching                                          |                    |

| RGB Switching                                                         | Page 41<br>Page 42 |

| On screen display                                                     |                    |

| CRT drive circuit                                                     |                    |

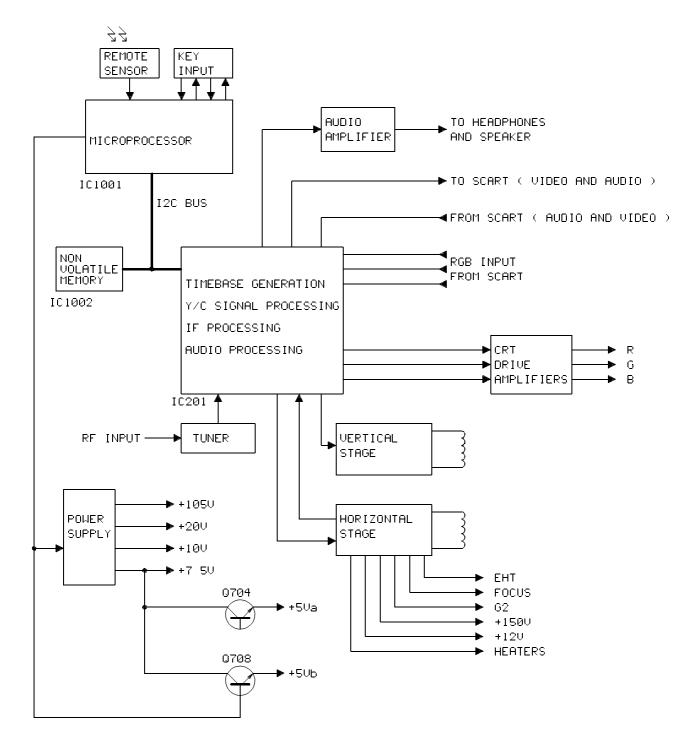

| Indiacting Devices                                                    | Dogo 11            |

| Indicating Devices                                                    | Fage 44            |

|                                                                       | Page 45            |

| I <sup>2</sup> C bus line disconnection                               |                    |

| Tuner                                                                 | Page 45<br>Page 45 |

| IC305 (Sound processor)                                               | Page 45            |

| SRS module                                                            | Page 45            |

| Shorting of SDA to SCL                                                | Page 45            |

| Disconnection of IC703 Power supply voltage line resistances to earth | Page 45            |

|                                                                       | raye 40            |

| Service Set Up Mode                                                   |                    |

|                                                                       |                    |

| Adjustments                                                           | -                  |

| Line                                                                  | -                  |

|                                                                       | -                  |

| CA1 Receiver Specifications                                           | Page 48            |

| CA1 Power Supply                                                      | Page 50            |

| Regulation Control Circuit                                            | Page 50            |

| IC201 Supply                                                          | Page 51            |

| CA1 Reset                                                             | Page 52            |

|                                                                       | -                  |

| Data                                                                  | Page 53            |

| CA1 Power On Control                                                  | Page 54            |

| CA1 Protection                                                        | Page 55            |

| Automatic Beam Current Limiting and X-Ray Protection                  | Page 55            |

| CA1 Discrete Component Vertical Stage                                 | Page 56            |

| Vertical Driver Stage                                                                                                                |                    |

|--------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| Frame Scanning Coils                                                                                                                 | Page 58            |

| CA1 Line Stage<br>Driver Stage                                                                                                       |                    |

| CA1 CRT Drive Amplifier                                                                                                              | Page 61            |

| CA1 Audio Output Amplifier                                                                                                           | Page 62            |

| CA1 Service Set Up Mode                                                                                                              | Page 63            |

| CA1 Non Volatile Memory Codes<br>CA1 NVM Locations and Functions<br>Procedure for Programming the NVM<br>NVM Programming Application | Page 64<br>Page 67 |

| Future Developments                                                                                                                  | Page 69            |

| Faults                                                                                                                               | Page 70            |

| Notes                                                                                                                                | Page 71            |

Produced by

Sharp Electronics (UK) Limited CE Technical Support Sharp House Thorp Road Newton Heath Manchester M40 5BE

Copyright © Sharp Electronics CE Technical Support Group November 1997

## Figures

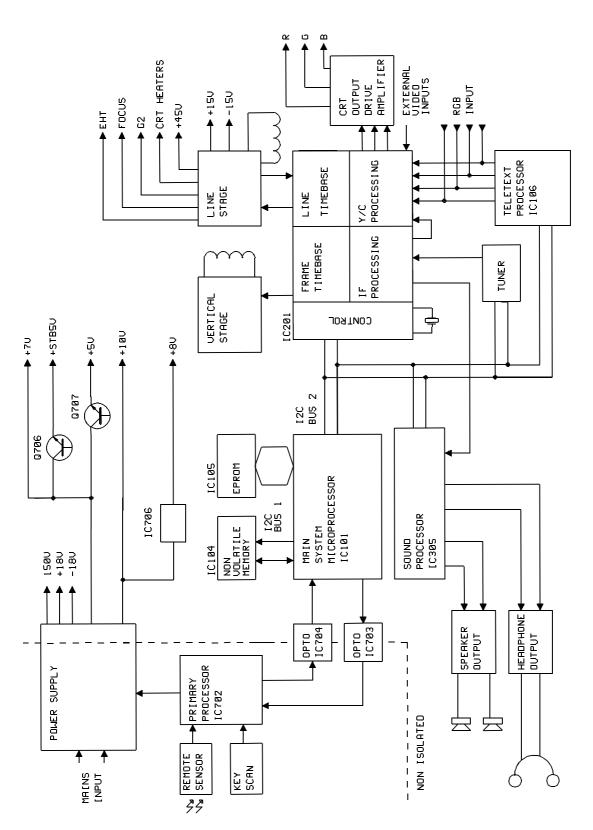

| Figure 1 : Overall Block Diagram of the CA10 Chassis        | Page 3  |

|-------------------------------------------------------------|---------|

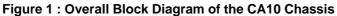

| Figure 2 : Mains Filter and Indicator Circuit               |         |

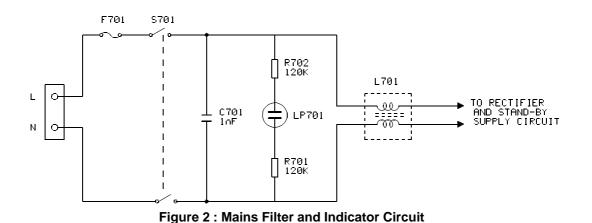

| Figure 3 : Mains Rectifier Circuit                          |         |

| Figure 4 : Power Supply Waveforms                           |         |

| Figure 5 : CA10 Power Supply - Non-isolated Side            |         |

| Figure 6 : Power Supply Regulation Circuit - Secondary Side | Page 8  |

| Figure 7 : Current Regulation Circuit                       |         |

| Figure 8 : Snubber Circuit                                  | Page 10 |

|                                                             | Page 11 |

| • • • • • • • • • • • • • • • • • • • •                     | Page 12 |

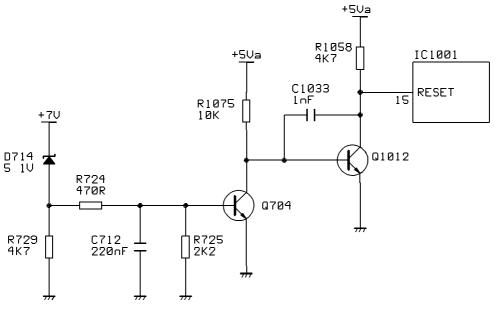

| Figure 11 : Reset Operation Circuit                         |         |

| Figure 12 : Reset Pulse Timing                              | Page 13 |

| Figure 13 : Data Communication of IC101                     | Page 14 |

| Figure 14 : Audio Protection Circuit                        | Page 15 |

| Figure 15 : Block Diagram of Line Stage                     | Page 16 |

| Figure 16 : Line Drive Circuit                              |         |

| Figure 17 : Line Output Circuit                             |         |

| Figure 18 : Line Current and Voltage Waveforms (Idealised)  |         |

|                                                             | Page 20 |

| Figure 20 : Sand Castle Pulse Detail                        |         |

| Figure 21 : Sand Castle Pulse Generation Circuit            |         |

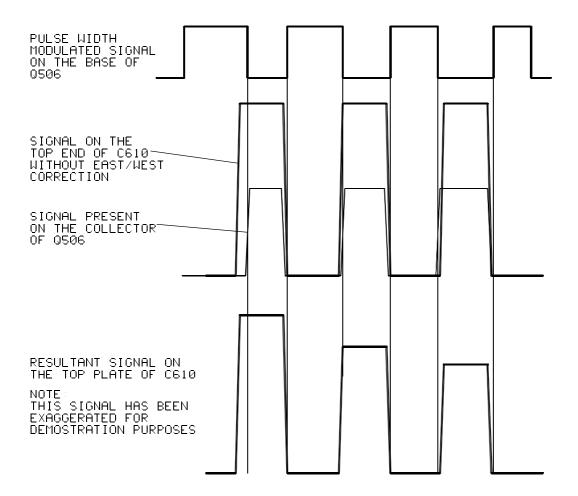

| Figure 22 : IC502 Ideal Waveforms                           |         |

| Figure 23 : Idealised East/west Pulse Waveforms             |         |

| Figure 24 : Diode Modulator Circuit                         |         |

| Figure 25 : East/West Drive Circuit                         |         |

| Figure 26 : Beam Current Limiter Circuit                    |         |

|                                                             | Page 25 |

| Figure 28 : Vertical Stage Block Diagram                    | Page 27 |

| Figure 29 : Vertical Drive Circuit                          | Page 28 |

| Figure 30 : Vertical Output Stage                           | Page 30 |

| Figure 31 : Tuner and IF Signal Path                        | Page 31 |

| Figure 32 : Video/Audio IF Split                            |         |

| Figure 33 : Spectrum of the Base Band Signal                | Page 34 |

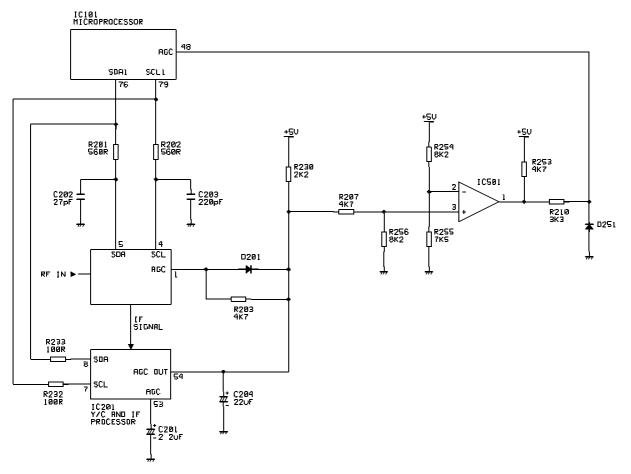

| Figure 34 : Automatic Gain Control Circuit                  | •       |

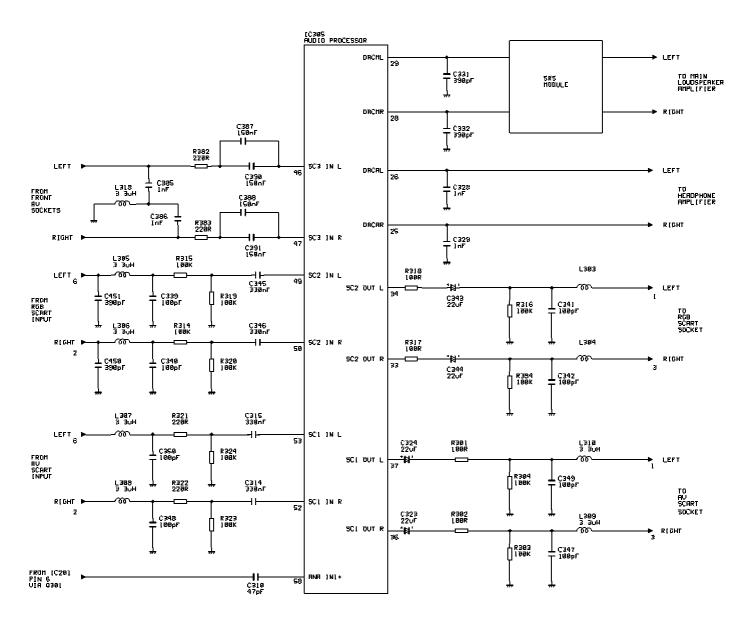

| Figure 35 : Audio Stage Circuit Diagram                     |         |

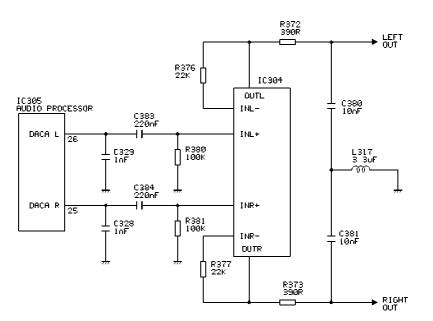

| Figure 36 : Headphone Amplifier Circuit                     |         |

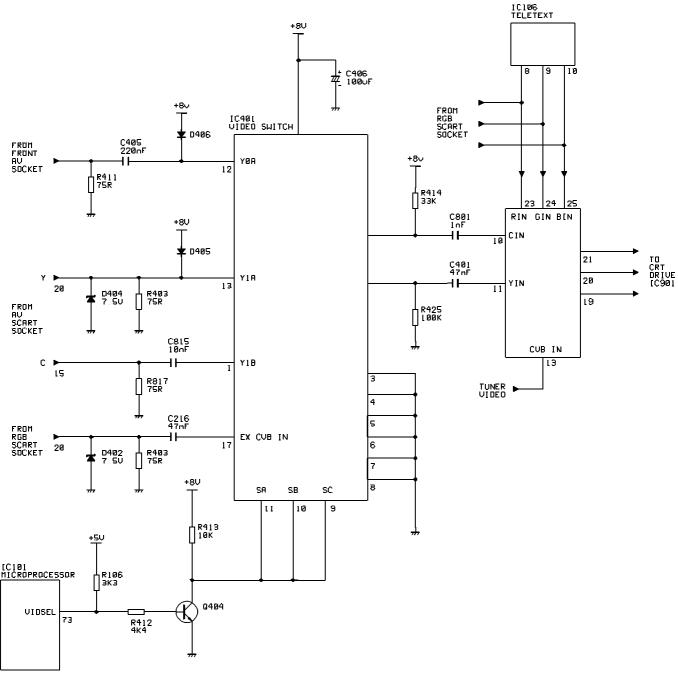

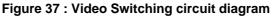

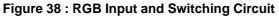

| Figure 37 : Video Switching circuit diagram                 |         |

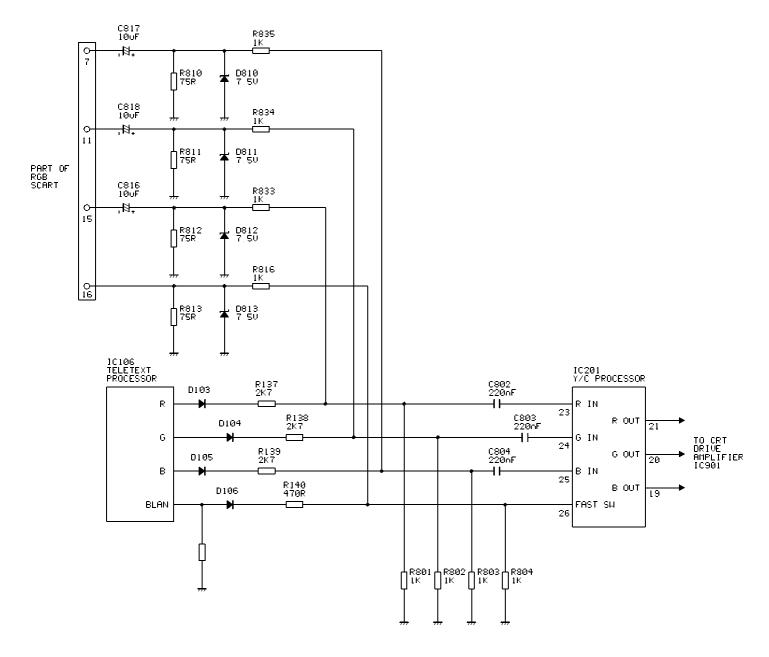

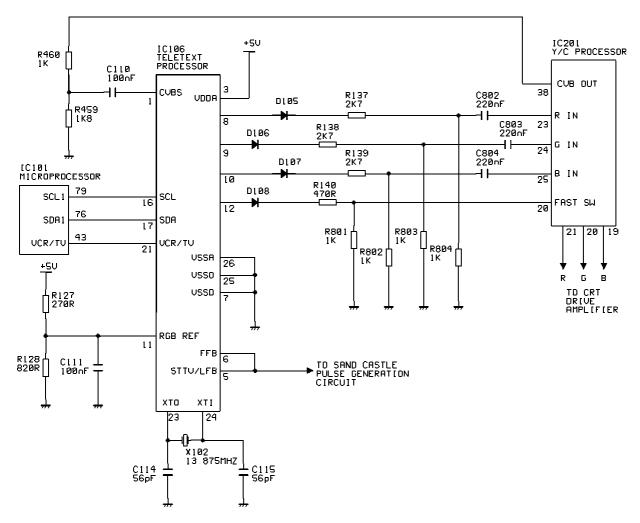

| Figure 38 : RGB Input and Switching Circuit                 |         |

|                                                             | Page 42 |

|                                                             | Page 43 |

| •                                                           | Page 44 |

|                                                             | Page 49 |

|                                                             | Page 50 |

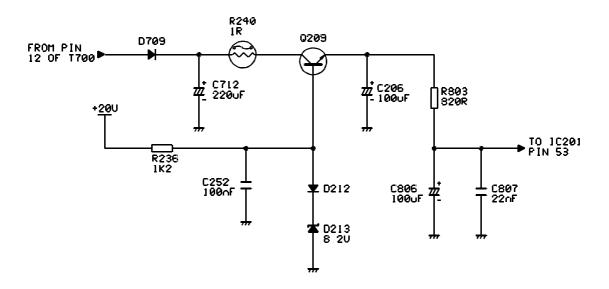

| Figure 44 : IC201 Power Supply Circuit                      | Page 51 |

|                                                             | Page 52 |

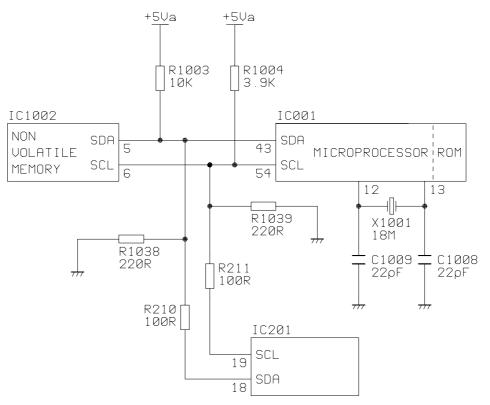

| Figure 46 : CA1 Data Communication                          | Page 53 |

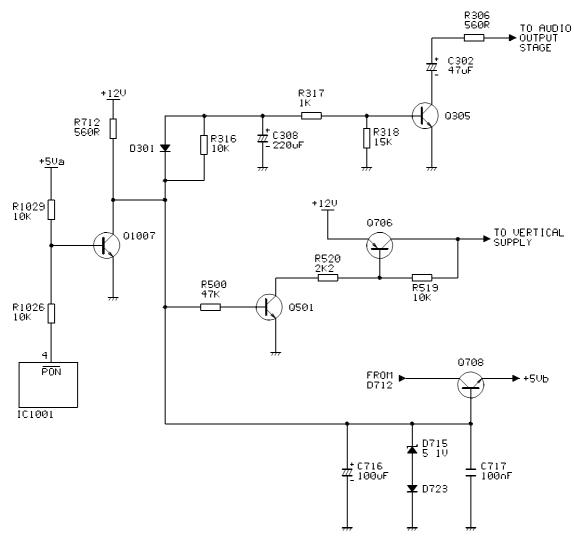

|                                                             | Page 54 |

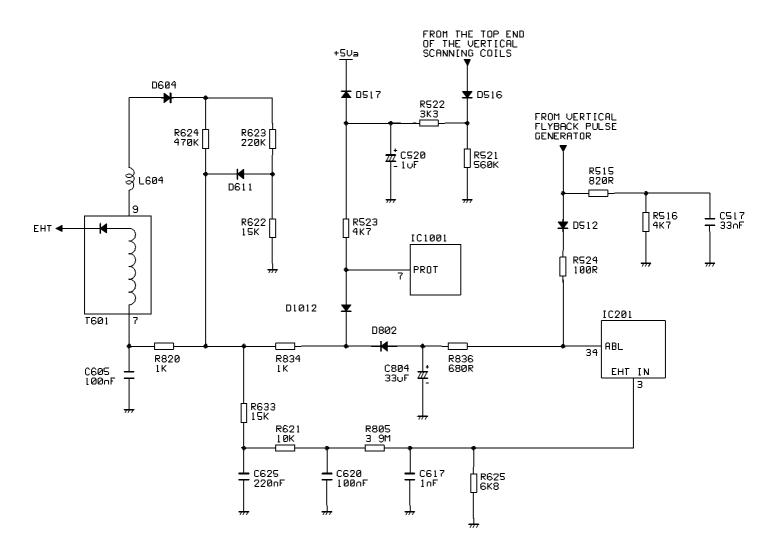

| Figure 48 : CA1 Protection Circuit                          | Page 55 |

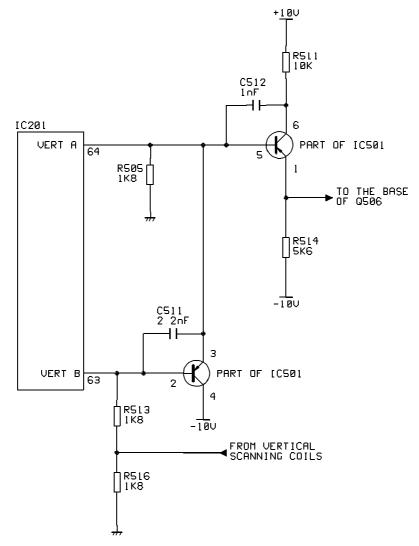

| Figure 49 : CA1 Vertical Driver Stage                       | Page 56 |

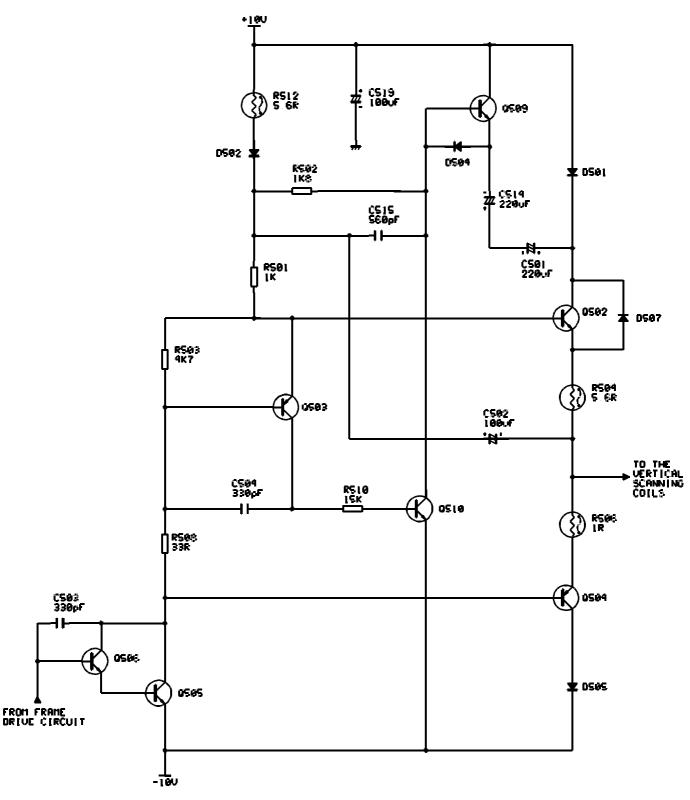

|                                                             | Page 57 |

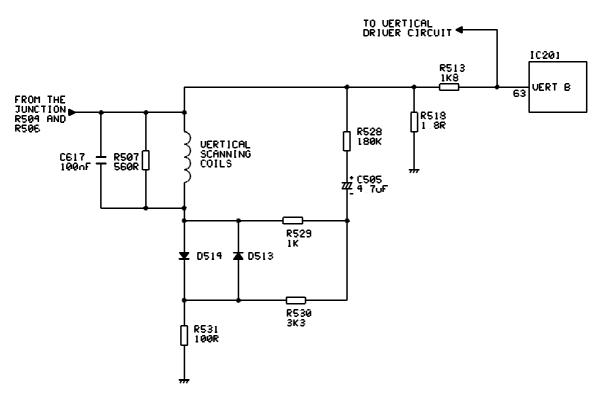

|                                                             | Page 58 |

|                                                             | Page 59 |

|                                                             | Page 61 |

| Figure 54 : CA1 Audio Amplifier Circuit                     | Page 62 |

## Introduction to the CA10 Chassis

As with the last Sharp colour television chassis (CS) the new CA10 design incorporates the latest technology from Japan and Spain where the receivers are designed and manufactured at the production plant in Barcelona.

Once again the reliable switched mode power supply, based around a field effect transistor, is used to provide power for the operation of the set. This has changed little since the CS chassis, but a detailed explanation of its circuit operation is given in the following pages.

Extensive use is made of dedicated integrated circuits and the number of surface mounted IC's is kept to a minimum to maintain an easier level of serviceability. The majority of IC packages are of the dual in line type. A break down of the major IC's explaining their basic functions is outlined below.

**IC101** is the only large surface mounted IC and provides overall system control.

**IC104** stores all the user information such as tuning and picture settings as well as geometry and CRT drive characteristics. This is an eight pin surface mounted device

**IC105** is the EPROM, which contains the program to run the main system microprocessor.

IC106 (STV5346) is a single chip teletext decoder/processor whose output is at RGB levels.

This

is a 28 pin surface mounted device.

$\ensuremath{\text{IC201}}$  ( TDA8844 ) provides the time base generators ( line and frame ), IF stage, majority of the Y/C processing and video switching ( including RGB ).

IC304 (M5218L) is the headphone amplifier.

**IC305** (MSP3410D) provides all the audio signal processing requirements, including decoding, volume control and signal switching.

IC401 (HEF4053) provides for video switching (including the Y and C signals).

**IC702** provides primary power supply on/off control and communication with the main system processor for key scan and remote control functions. It also controls the receivers self timer operation.

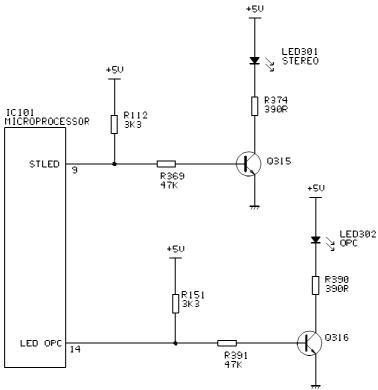

IC901 (TDA6107Q) drives the CRT.

Note that IC101 and IC702 are produced by Sharp and therefore can only be obtained through the Sharp Spare Parts Centre. IC104 and IC105 are generally available, but contain programs and therefore must also be obtained direct from Sharp Spare Parts Centre.

As the tuner is directly controlled by the I<sup>2</sup>C bus it enables direct channel entry and stable control of the tuning and AFT functions. By receiving controlling inputs from IC201 (IF processor) and IC106 (teletext processor) the main system processor can carry out automatic tuning and sorting.

Various audio inputs can be used to generate either mono, stereo or SRS (Sound Retrieval System) sound, depending on receiver specification - see next page for model specifications. Output from the top of the range receiver is 2 x 20W (MPO) and an additional 20W from the external sub-woofer. As the audio signal is controlled by the data bus, it is possible to have separate control of both loudspeaker and headphone outputs.

Video switching from a number of sources is possible, this includes RGB from a rear SCART socket and S-VHS from the rear AV SCART socket.

All of the above contribute to make a reliable and easily repairable television chassis, that is fitted into all of the new Sharp range of large screen television receivers as listed on the following page.

## CA10 Receiver Specifications

The table below lists all of the current range ( as of January 1998 ) of Sharp television receivers utilising the CA10 chassis. Note that the receivers featuring a sub-woofer will have an extra drive PWB fitted and the SRS models will have the SRS sound processing sub PWB fitted.

| Features              | 51DS02H  | 51DS03H  | 51DS05H  | 59DS03H  | 59DS05H  | 66DS03H  | 66DS05H  |

|-----------------------|----------|----------|----------|----------|----------|----------|----------|

| Tube Size ( inches )  | 21       | 21       | 21       | 25       | 25       | 28       | 28       |

| Visible Screen ( cm ) | 51       | 51       | 51       | 59       | 59       | 66       | 66       |

| Tube Type             | B Matrix |

| Number of Pre-sets    | 99       | 99       | 99       | 99       | 99       | 99       | 99       |

| Auto Sort             | Yes      |

| Fast Text             | Yes      |

| NICAM                 | Yes      |

| SRS/3D Sound          | -        | -        | Yes      | -        | Yes      | -        | Yes      |

| AI-OPC                | -        | -        | Yes      | -        | Yes      | -        | Yes      |

| On/Off Timer          | Yes      |

| Rear S-VHS Input      | -        | -        | Yes      | -        | Yes      | -        | Yes      |

| 21 Pin Euroscart      | 2        | 2        | 2        | 2        | 2        | 2        | 2        |

| Ext Speaker Output    | -        | -        | -        | -        | S Woof   | -        | S Woof   |

| Power Output (MPO)    | 2x4      | 2x10     | 2x10     | 2x10     | 2x10+20  | 2x10     | 2x10+20  |

| Headphone Jack        | Yes      |

| Stand                 | Yes      | Yes      | Yes      | Yes      | -        | Yes      | -        |

| Cabinet               | -        | -        | -        | -        | Yes      | -        | Yes      |

| Width ( mm )          | 539      | 612      | 612      | 695      | 695      | 740      | 740      |

| Height (mm)           | 468      | 458      | 458      | 537      | 537      | 566      | 566      |

| Depth (mm)            | 484      | 492      | 492      | 431      | 431      | 470      | 470      |

| S/B Power             | 3W       |

#### Note :

Sharp reserve the right to make design and specification changes for product improvement.

The performance specification figures are nominal values of production units. There may be some deviation from these figures in individual units.

To complete this range of television receivers, the CS chassis is used for the Dolby Pro-logic models 59CSD8H and 66CSD8H.

## CA10 Block Diagram

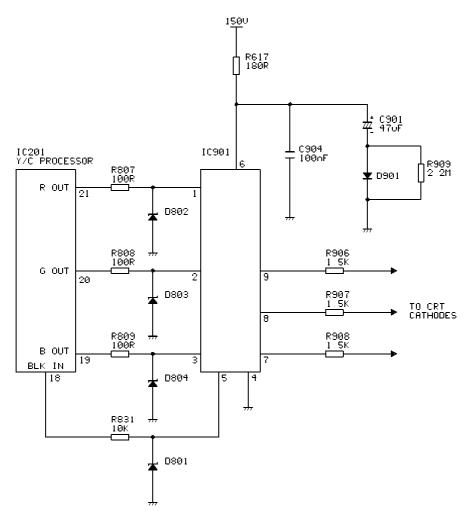

To give an overview of the CA10 Chassis, the block diagram shown below represents a pictorial view of the receiver and its individual components.

## **Power Supply**

16

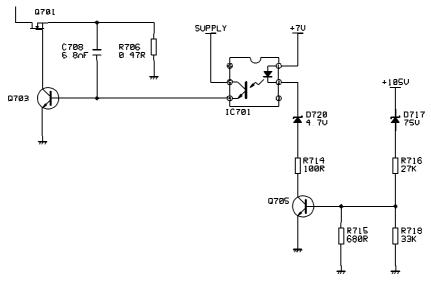

This self running switched mode power supply is based around a single field effect transistor, Q701 and generates the following supplies for use in various parts of the receiver. Note that other supplies are generated by the line stage and are covered in the **Line Stage** section of these notes.

| Supply | Purpose                                                 | Point of Generation |

|--------|---------------------------------------------------------|---------------------|

| +18V   | Audio and frame output amplifiers                       | D718, pin 8 of T701 |

| -18V   | Audio and frame output amplifiers                       | D719, pin 8 of T701 |

| +150V  | Line output, CRT drive amplifier and VT line generation | D720, Pin 4 of T701 |

| +13V   | Source of +8V supply                                    | D711, pin 5of T701  |

| +8V    | IC201 supply                                            | IC706               |

| +7V    | Source of STB5V and 5V                                  | D722, pin 1 of T701 |

| STB5V  | Supply for IC101/2/5/6                                  | Q706                |

| +5V    | Supply for IC305, tuner                                 | Q707                |

**Note** : The voltages attributed to the rails on the circuit are not necessarily the measured voltage. See the **Power supply voltage line resistances to earth** section of these notes for actual measured voltages and nominal cold resistances to ground.

#### Mains input circuit

From the mains plug (fitted with a 3A fuse), the mains passes into the set via connector GN0304 and into the fuse, F701 (3.15A anti-surge). After the mains switch, S701, the mains applied indication neon is connected across the live and neutral lines via R701 and R702. From this point the mains is fed to the de-gauss circuit, via L701 and the positor POR701, undesirable spikes generated by the de-gause operation, are removed by C702. Choke L701 provides further noise suppression. After L701 the mains is also sent to the standby control circuit. Finally, after passing through L702 and L703, the mains is supplied to the bridge rectifier.

Figure 3 : Mains Rectifier Circuit

D701, D702, D703 and D704 full wave rectify the incoming mains and this rectified voltage is smoothed by C705. The resultant 320VDC is now fed to the switched mode power supply.

D705 is used to limit possible damage caused to the bridge rectifier from internally generated noise that could come close to the PIV of the diodes. Note that in some versions of the CA10 chassis, this diode is not fitted.

#### Standby operation

Because of proposed legislation, which will limit the stand by power consumption, changes have been made to the operation of the set during the stand by mode. This is achieved by muting the operation of the power supply in the standby mode so that no oscillation takes place. The operation of the power supply described below, therefore, relates to when the set is running. How the set comes out of standby will be covered in the **Power on control** section of these notes.

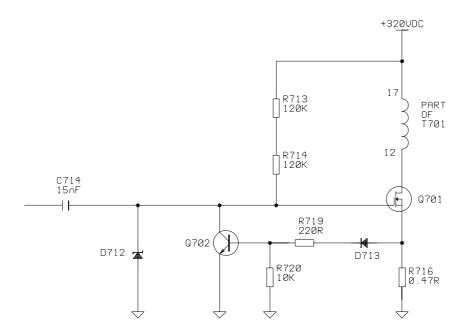

#### Start up operation

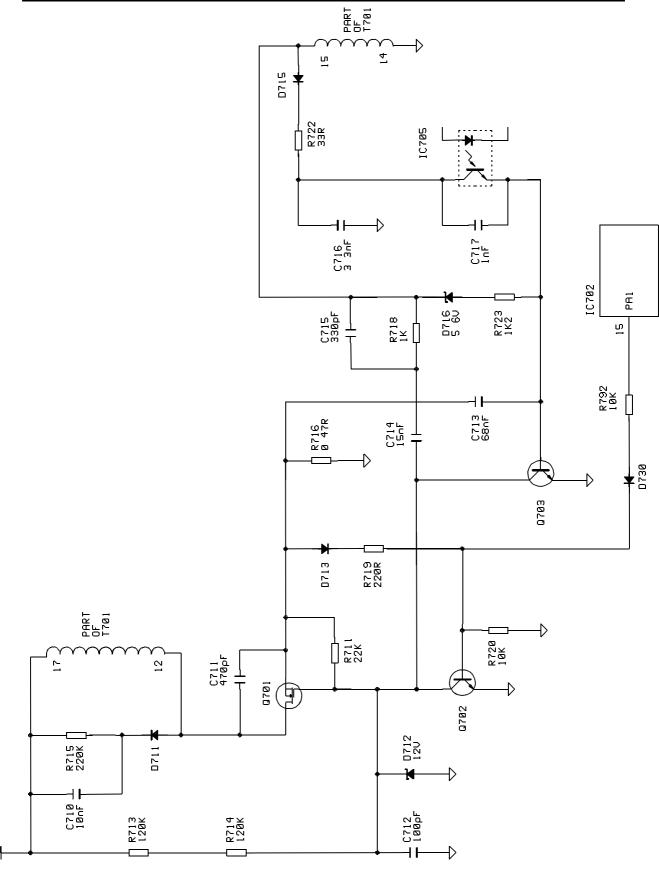

Rectified and smoothed mains voltage (+320VDC) is used to provide the start up voltage to the gate of Q701. Current flows via R713 and R714 causing C714 to charge up, the earth return for the capacitor is via R718 and winding 15/14 of T701. This allows a voltage to be built up on the gate of Q701 ( this will turn on Q701 when it gets to about four and a half volts). D712 ensures that the steady DC on the gate of Q701 does not exceed twelve volts as any voltage higher than this may damage the device. C712 removes any high frequency pulses that may damage Q701.

As Q701 turns on, current will flow via the bridge rectifier, pins 17 and 12 of T701 and the source/drain of Q701 finally returning to the bridge rectifier by the earth return resistor, R716. This will induce an emf into the primary winding of the chopper transformer, which will be reflected by the secondaries via the magnetic induction within the transformer itself.

The voltage generated by the winding connected between pins 14 and 15 will also increase as the conduction of Q701 increases. This increase in voltage will cause D716 to conduct when its zener voltage is reached (5.6 volts). Therefore C713 will start to charge and when the base/emitter voltage of Q703 reaches 0.65 volts it will conduct and effectively remove the gate supply. Q701 is now turned off and current ceases to flow in the primary winding of T701 and the emf will start to decay.

As the secondary voltages decay, pin 15 of T701 will go negative and this negative charge is transferred via C714 to the gate of Q701, holding the FET fully off for a time period decided by the charging rate of C714 (via R713/4) and the discharge rate of C713 (via the base/emitter junction of Q703). Once the magnetic field has collapsed totally, the cycle is repeated.

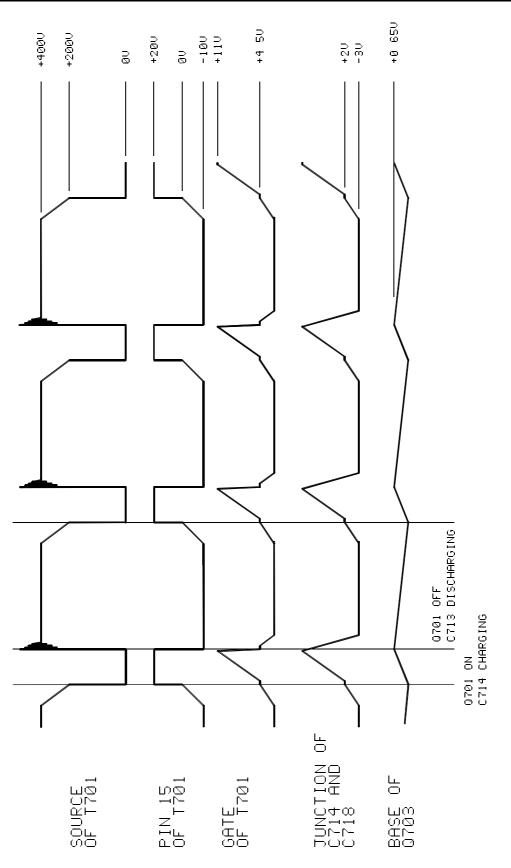

Figure 4 : Power Supply Waveforms

320000

Figure 5 : CA10 Power Supply - Non-isolated Side

Figure 6 : Power Supply Regulation Circuit - Secondary Side

#### Voltage regulation

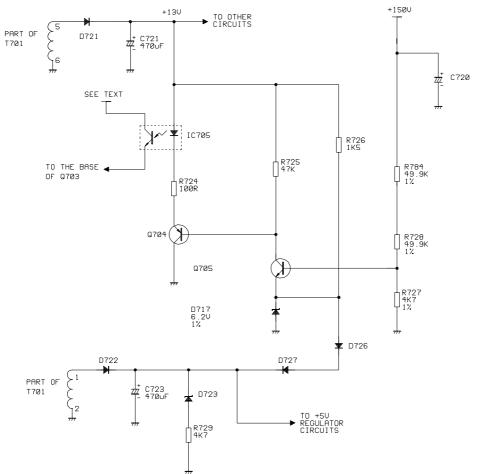

Voltage regulation is provided by the feed back through the opto coupler, IC705. The 150 volt line is used as the controlling source and a reference is provided from the +13V supply. Protection is also incorporated via the +7V supply for faults that may occur on either of the five volt supplies (STB5V and +5V).

Current flowing through the opto coupler LED will effect its brightness and therefore the conduction of the light sensitive transistor. This will control the time taken to charge C713 from the supply generated by D715 and R722 and therefore will control the turn on time of Q703, note that the earth return for C713 is via R716.

As the collector of Q703 is connected to C714 this action will in turn affect its charging time and the on/off time of Q701. As the charge/discharge of C714 is controlled by the switching of Q701 its base capacitor, C713, is the timing control influence. As the discharge of C713 is constant, the off time will remain at approximately the same period during each cycle, because its discharge path remains the same through R716. Whereas the charging of C714 will control the on time, i.e. when its charge is above the threshold turn on voltage on Q701 or +4.5V. Therefore it can be noted that an increase in load will slow down the frequency of operation.

Note that D715, R722 and C716, on the primary side of the opto coupler, provide a voltage supply circuit to the collector of the transistor contained within IC705. Also note that on the secondary side of the regulation circuit, the supply for the reference zener diode, D717 is taken from the +13V supply.

#### Supply increase

If the 150 volt supply line were to increase, the voltage on the base of Q705 would also increase. As the emitter of Q705 is held steady by the zener diode D717, at 6.2V, the collector will start to drop. This

will allow Q704 to conduct more and the LED will become brighter.

As the LED becomes brighter, the transistor within IC705 will conduct more allowing C713 to charge faster and thus turning on Q703 quicker. Q703 will discharge Q714 and turn Q701 off, making the on time of Q701 shorter. The emf will decrease and the voltages induced in the secondary windings of T701 will also decrease.

#### Supply decrease

If the 150 volt supply line were to decrease, the voltage on the base of Q705 would decrease. As the emitter of Q705 is held steady by the zener diode D717, at 6.2V, the collector will start to rise. Q704 will conduct less and the LED will become less bright.

As the LED becomes less bright, the transistor within IC705 will conduct less giving a lower voltage on the base of Q703 and C713 will charge more slowly. Q703 will now turn on later in the cycle and allow C714 to charge up for longer. This will turn on Q701 for longer and the current through the primary winding (12 and 17) of T701 will increase. The emf will increase and the voltages induced in the secondary windings of T701 will also increase.

#### Note

The voltage present at the junction of R784/R728 and R727 will be exactly 6.7464V when the supply is 150V. As the emitter of Q705 is held at 6.2V by the action of zener diode, D717, the collector will follow the base voltage. As the  $h_{fe}$  of Q705 (2SC2412) is high it will amplify the voltage on its base so that the voltage swing on its collector will be great enough to vary the base voltage of Q704 dramatically. Q704 is effectively a current amplifier which allows the LED inside the OPTO coupler to be driven through its range of intensity.

C720 ensures that no short time constant variables effect the operation of the regulation circuit. If the regulation were to change too quickly, there may be a chance that the power supply will oscillate at a high frequency - this is undesirable.

As the tolerances in this part of the circuit are high and impedances are also relatively high, there is a risk of circuit malfunction if a voltmeter with too low an impedance is used. In worst case this could lead to failure of the power supply. It is recommended that if fault finding has to be carried out in this part of the circuit, then an oscilloscope is used.

#### Protection

Protection is provided should one of the five volt supplies, STB5V and +5V, drop to an unacceptable level. This is achieved by monitoring the +7V supply which is used to generate the STB5V and +5V lines.

Should the +7 volt supply drop to a point whereby diodes D726 and D727 start to conduct, the voltage on the emitter of Q705 will drop. This will cause the collector of Q705 to drop, turning Q704 on harder, making the LED brighter and turning on Q703 sooner, dramatically decreasing the discharge time of C714 and thus the ON time of Q701. Therefore reducing the current flowing in the primary winding of T701.

When the current flowing in the primary winding of T701 decreases, so will the secondary voltages. This will cause the voltage generated by D722 (+7V rectifier) to also drop. This will reinforce the above action and the power supply will attempt to shut down. During this cycle, there will come a point where it becomes impossible to maintain the conduction of Q703 ( as the charge on C713 decays to below +0.65V) and the power supply will start up again. If the condition of the +7V ( low supply ) line continues the set will continually trip.

#### **Over current control**

Over current control is performed by monitoring the amount of current passing though the chopper output transistor drain earth return resistor, R716. This resistor is an extremely low value, 0.47R, and Ohms Law dictates that the current flowing through it must be proportional to the voltage across it. If the base voltage required to turn on Q702 is +0.65V then the voltage across R716 to 'trip' the circuit would have to be approximately 1.2V (if the volt drop across D713 was 0.6V). This results in a trip current through R716 of 2.55A.

The voltage developed across R716 is used to turn Q702 on via D713 and potential divider, R719/20. If Q702 turns on it will discharge C714 rapidly removing the gate bias and Q701 which will turn off until the current trough R716 decreases to a point where Q702 turns off and Q701 turns on again ( after C714 has charged up to four an a half volts ). In the case of heavy current over load this will cause the power supply to whistle as the frequency of the power supply stopping and starting will be within the audio range.

Figure 7 : Current Regulation Circuit

D713 is used to set the voltage / current (through R716) at which Q702 will initiate an "over current" action. Therefore, the smaller screen sizes fitted with the CA10 chassis may not have this diode in the circuit shown above

#### **Snubber circuit**

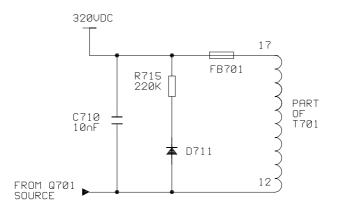

Figure 8 : Snubber Circuit

When the magnetic field within T701 collapses, the back emf generated across the primary winding causes large voltage spikes to appear across pins 12 and 17. If these spikes are not suppressed, then damage will occur to the primary side of the power supply.

To prevent this from happening a snubber circuit, consisting of D711, R715 and C710 is used. Thus when pin 12 becomes positive with respect to pin 17, D711 will conduct and current will flow through R715. The spike will be damped by the action of C710 and R715. FB701 removes any HF noise.

#### Power on control

Primary processor power supply

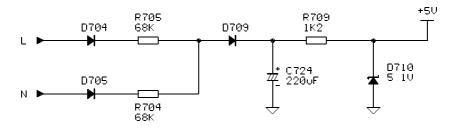

As the chopper supply stage is shut down during the standby mode, it is necessary to provide power to the control circuitry from another source. This is achieved by supplying the mains voltage to a shunt regulator circuit as shown in the diagram below.

Figure 9 : Primary Processor Power Supply

This simple circuit provides a positive five volt supply to the reset IC, IC701 and microprocessor, IC702.

#### Power supply turn on

At mains application, the primary microprocessors reset IC, IC701, will provide a positive going reset pulse to initialise IC702. At the same time the ceramic filter, CF701 will start to oscillate. This sequence of events will initialise IC702, the key scan and remote control function will become operational.

When pin 15 ( PA1 ) of IC702 goes low, either by pressing one of the four buttons on the front of the television or by use of the remote control, the base bias to Q702 will be removed and it will turn off, its collector voltage will therefore rise. The power supply will now start up in line with the description given previously.

If pin 15 (PA1) of IC702 goes high, it will turn on Q702 via R792 and D730. This action will remove the voltage on the gate of Q701 and turns it off. As this condition is permanent (for the period of time that pin 15 is at five volts), the power supply will turn off until a new power on command is issued by IC701...

Communication is maintained with the system microprocessor, IC101, via the two opto couplers. IC704 is used to send data from IC702 to IC101 for control purposes - button pressing and remote control. IC703 is used to control IC702 from IC101, i.e. to shut down the set if a protection fault occurs. Note that the reset pin of IC701 is also connected to this opto coupler via D706, so that if the transistor conducts heavily, pin 6 of IC702 will go low. IC702 will now turn the power supply off which will remove the supply to the main processor and IC703 will stop conducting therefore pin 6 will be allowed to rise, resetting IC702 and in turn powering up the supply again. Note that the supply to IC702 is always there.

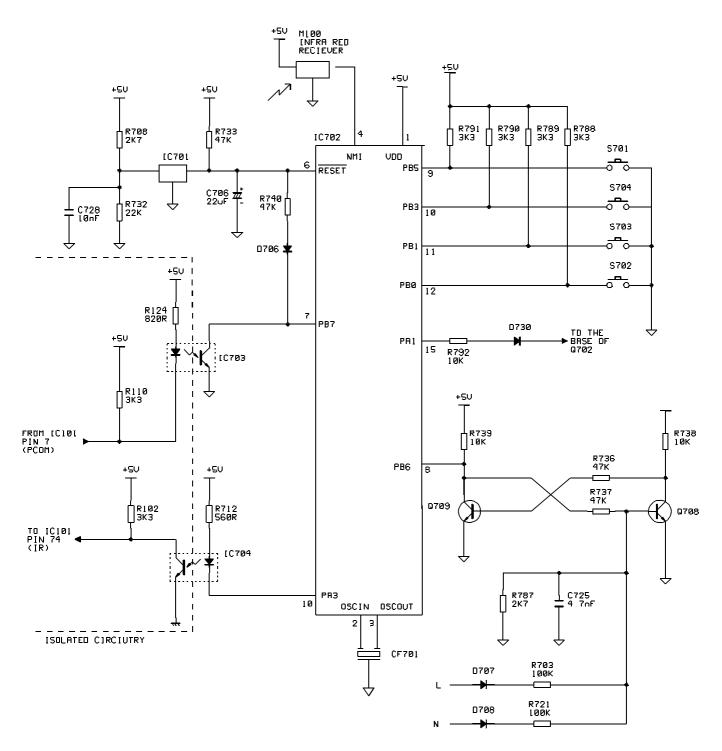

## **Primary Processor**

As described previously, to control the operation of the set in the standby mode a primary processor is utilised. The circuit diagram of this part of the circuit is shown below.

The two transistors Q708 and Q709 comprise a monostable, which is triggered from the mains input at double frequency, i.e. 100Hz. The square wave signal on pin 8 (PB6) is used to control the on timer. This is necessary due to the fact that in standby, the main system microprocessor, IC101, is dormant, i.e. no supply and therefore can not perform any functions. The off timer function is controlled within IC101.

## **System Control**

#### **Resets and oscillators**

When the power supply starts up the program within the main microprocessor needs to be reset. This is achieved with the use of the circuit shown below.

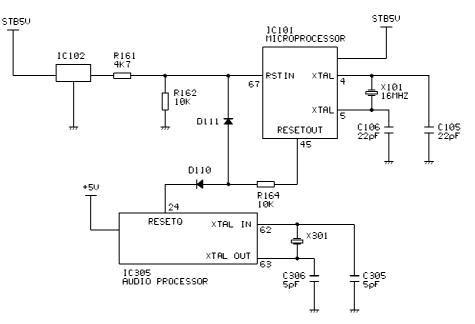

Figure 11 : Reset Operation Circuit

When the STB5V supply has reached its correct level, the output from IC102 changes from a low to a high level to reset IC101 on pin 67 (RSTIN). After IC101 has reset itself it gives a further reset to the audio processing IC, IC305 via pin 45 (RESETOUT). This pin changes from low to high, then back to low and finally remains high as shown in the diagram below. IC305 is now reset.

Figure 12 : Reset Pulse Timing

Once the main system microprocessor, IC101, has reset and the oscillator is running at the correct frequency the internal programme sequence is initiated. It first checks that the internal functions of the IC are working correctly then checks the devices connected to it via the  $I^2C$  bus. If any errors are encountered then the microprocessor will either shut down or produce a fault symptom - see the  $I^2C$  bus line disconnection part of these notes for more details.

When the microprocessor has satisfied itself that all devices connected to it are operating correctly, it will read information from the EEPROM, IC105, to operate the set in the right sequence.

#### Data communication

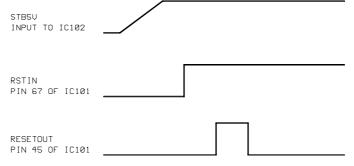

Within the CA10 chassis, there are a number of data control signals that pass to and from the main system microprocessor, IC101. There are two basic types, serial and parallel as shown in the diagram below.

Figure 13 : Data Communication of IC101

#### I<sup>2</sup>C bus

There are two I<sup>2</sup>C buses used to communicate serial information to and from IC101. SDA1 and SCL1 is used to communicate with IC106 (Teletext processor), IC305 (Audio Processor), IC201 (IF, signal and time base processor) and the tuner. Each feed is current limited from the processor by the use of resistors (except for the teletext processor which is connected directly). Isolating these lines can be useful for fault finding - see the **I<sup>2</sup>C bus line disconnection** section of these notes for more details.

The other I<sup>2</sup>C bus is used for exclusive communication with the non volatile memory, IC104. IC104 contains all the user default values such as tuning information and picture control settings as well as geometry settings, grey scale information, chassis operating characteristics (text, NICAM etc). As this IC may be corrupted by glitches on the communication lines, D113 and D114 are used to suppress any spikes greater than 5.6 volts that may appear on the clock and data lines.

#### Parallel communication

Parallel communication exists between the EPROM and the microprocessor. The EPROM is where the main programme to run the various functions of the set are held eg Text programme, NICAM programme. As it is necessary for the processor to have fast access to this data, it is connected via a sixteen bit address line. The data is carried on an eight bit line.

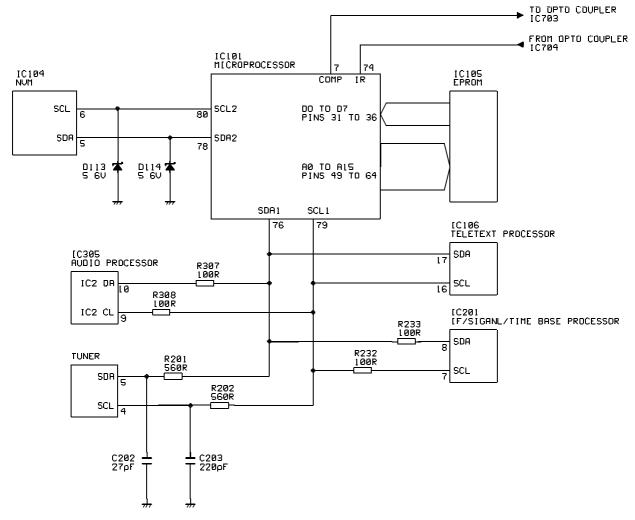

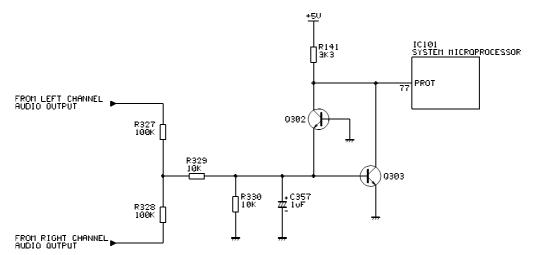

#### **Protection circuits**

There is a protection input on IC101, pin 77 (PROT) which causes the set to shut down should there be a fault with the audio output stage.

When the audio output is operating correctly, the feed to the loudspeaker will have an average DC level of zero volts. If an imbalance were to occur whereby the signal became predominately more positive or negative, this could lead to failure of the audio output devices or loudspeaker. To alleviate this possible problem, the circuit shown below is used to turn off the set should the situation arise.

Figure 14 : Audio Protection Circuit

Under normal conditions, both Q302 and Q303 are turned off and the voltage present on pin 77 of IC101 is held high by the 3k3 pull up resistor R141. Should one of the outputs go more positive, then the DC level developed across C357 will increase. If this increase exceeds 0.6V, then Q303 will turn on, pulling down pin 77 and shutting down the set.

If one of the outputs were to go too negative, then the charge on C357 would drop, if this drop is greater that -0.6V then Q302 will conduct on pin 77 will be pulled low. Thus the set would shut down.

#### Software reset

As with the previous large screen chassis, the NVM is down loaded with its default information when the set is first powered up after manufacture. This means that whenever a NVM is ordered, it will be the same for all types of chassis ( previous NVM's have come pre-programmed for the receiver in question ).

If the information within the NVM is corrupted or settings/adjustments can not be made, then it is necessary to re-initialise the NVM. This is done using the following procedure.

- 1. Enter the service mode by pressing the channel down and volume up buttons on the front of the receiver, while turning on the mains power. Note that the two buttons have to be kept pressed until the receiver turns on.

- 2. Select the NVM position 00.

- 3. Set this location to 01.

- 4. Store the information by pressing the stand by button on the remote control.

- 5. Turn the set off at the mains.

- 6. Turn the receiver back on. It will take about thirty seconds for the receiver to start up as the microprocessor is down loading the information into the NVM.

Some settings may need sight adjustment as the preset values are based on no tolerance settings , in reality some will vary. Note that the above location of 00 is for the CS chassis type, to date this location for the CA chassis is unknown. Please consult your Technical Liaison Officer for more details.

## Line Stage

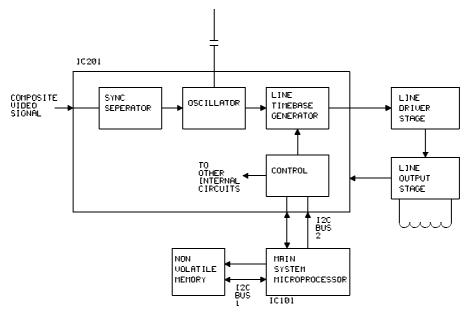

Line signal generation is carried out within IC201, with synchronisation being supplied by the incoming sync pulse. The line stage generates various supplies, including EHT, focus, G2, A1 and heaters and the line scan coil drive signal.

Figure 15 : Block Diagram of Line Stage

#### Line time base generation

IC201 generates the line drive signal internally using an oscillator whose frequency is controlled by various external components, the output of this oscillator is approximately 15.625kHz. Synchronisation is taken from the incoming video signal (tuner or video inputs) line synchronisation pulse when a signal is being received, in all other cases the oscillator is left to free run. When free running the on screen display is locked internally by comparing the sand castle pulse with the graphical information.

When the set is first turned on, using the standby button, the line oscillator runs at twice line speed - 31.25kHz. IC 201 then monitors the feed back from the line stage on pin 41 (SCL). When this signal is correct, the oscillator switches to 15.625kHz. The reason for this is so that the capacitors on the secondary windings of the line output transformer charge up faster to enable the line stage to reach its optimum operating characteristics quickly. This will prevent any excessive strain being put on the windings of the line output transformer. It is also necessary as the line drive circuit uses secondary supplies from T601 to ensure that the output transistor is turned hard on, if the line speed was not doubled then the set would not have enough energy to start up.

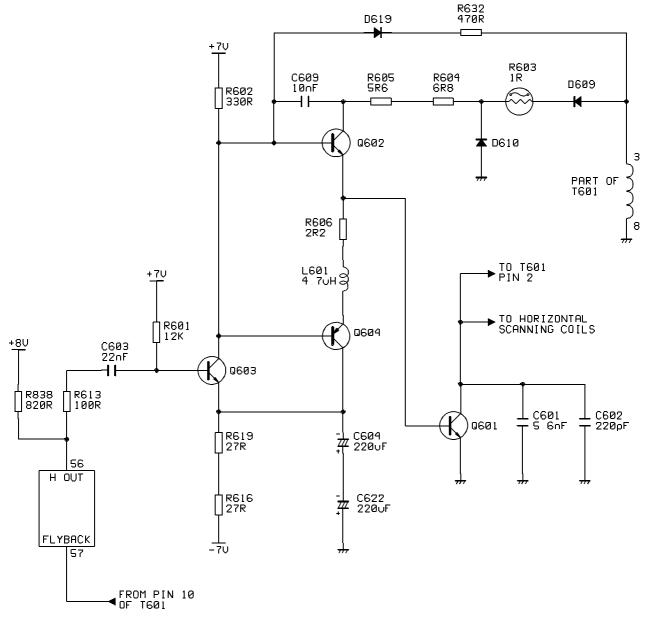

#### Line drive circuit description

The line drive circuit does not use a conventional coupling transformer, but is instead directly coupled to the drive IC as shown in the diagram on the next page.

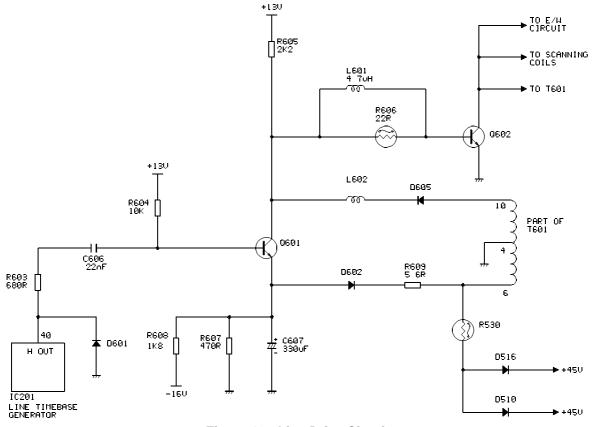

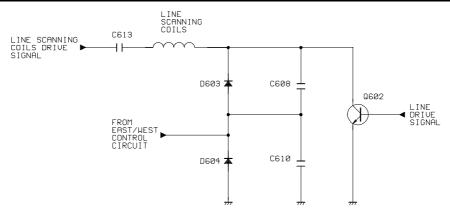

From pin 40 of IC201 (HOUT) the line drive signal is fed through the DC blocking capacitor C606 into the base of Q601. D601 prevents any spikes that may appear on the drive signal from damaging the rest of the circuit. R604 pulls up the base of Q601 to the +13V supply.

As the line drive starts up at 31.25kHz, there will be no voltages generated by the line output stage to enable the line driver circuit to operate correctly. Therefore a feed is taken from the +13V and -16V lines off the chopper stage. In this situation, when Q601 is on the base of Q602 will be taken low (+13V plus -16V giving -3V) and Q602 will not conduct. When its base goes high, Q602 turned off, its collector current will start to rise, but this rise is limited by a number of factors. First is R605 and the second is the current drawn by Q602 itself. Both of these conditions mean that the base of Q602 never exceeds 0.65V. As Q602 conducts an emf will be generated in the secondary winding of pins 4, 6 and 10.

Once IC201 has detected a feed back pulse, it will switch the line drive signal frequency to the correct running rate of 15.625kHz. At this point the supplies from the chopper stage are not used and those generated by the flyback transformer, T601, will take over.

As the current drawn by the base of Q602 is proportional to that drawn by its collector, it is desirable to have a low impedance source to drive its base ( hence the use of a coupling transformer in a conventional line driver circuit ). In this chassis a base current of four to five amps ins not unusual, and therefore a low impedance source need to be provided, which in this case is provided by the winding 4 to 10 of T601.

Assuming that the line has started up, when Q601 is off the current to turn on Q602 will flow from pin 10 of T601, through R605, L602 and L1/R606 into the base of Q602. This will turn on the device and current will flow in the primary winding of T601.

When Q601 is turned on, the current that would normally flow into the base of Q602 is now diverted through Q601's collector/emitter junction. This will turn off Q602 as its base voltage will drop below 0.65V. In actual fact the base voltage of Q602 drops to about -10V.

As can be seen from the diagram, pin 6 of T601 also generates the +45V supply used in the east/west correction circuit, but the voltage on the anode of D602 is negative. This is due to the fact that the waveform appearing at pin 6 is over 50V in the positive direction, but only about -15V in the negative direction ( mainly overshoot ). It is this negative going waveform that is rectified to produce the turn off voltage for Q602.

Figure 16 : Line Drive Circuit

R606 and L601 couple the line drive signal generated by Q601 to the base of the output transistor, Q602. These components are necessary to ensure that the transistor is fully saturated. They also, to some extent, provide protection to Q601 and IC201 should the output transistor go short circuit and allow excessive current and/or voltage to appear on its base.

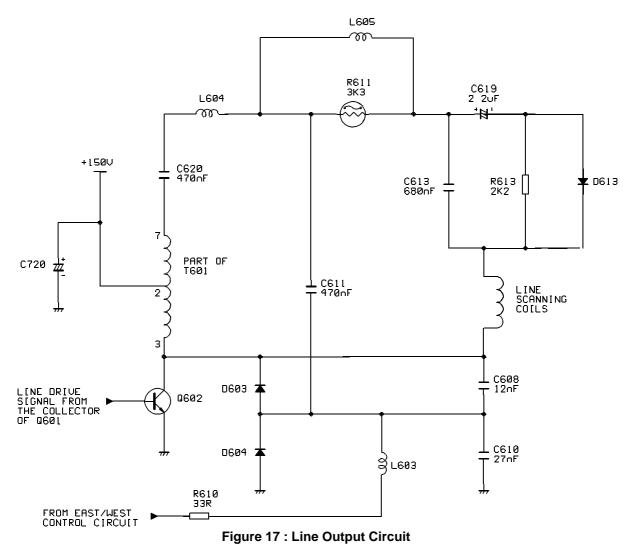

#### Line output circuit description

To enable enough emf to be generated by the line stage in this 59/66cm chassis, it is necessary to provide a high HT voltage of 150VDC. This is fed into the line output transformer, T601, at pin 2 as shown in the diagram below, note that there is no feed resistor into the transformer.

From the collector of the drive transistor, Q601, the line drive signal is fed into the base of Q602. This is a square wave signal that turns on for 26uS and off for 38uS.

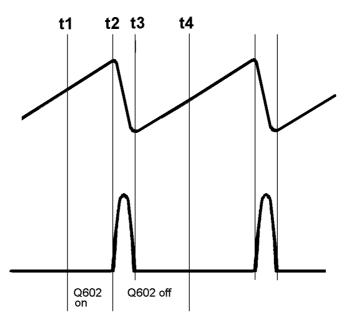

When Q602 is turned on, current will start to flow in the primary winding of T601 (pins 2 to 3), this is point t1 in the current waveform shown on the next page. This current flow will continue to increase until Q602 is turned off some 26uS later, at which point the current in the primary winding will start to decay, point t2. The time taken for this current to decay is determined by the time constant of the primary winding and C608 (for the purpose of this explanation the bottom end of C608 and D603 can be considered to be ground and C610/D604 ignored). This charging current is supplied from the HT reservoir capacitor, C720, which will effectively connect pin 2 of the transformer to ground (for ac purposes).

At the point where the current starts to drive negative, t3, the clamp diode, D603 will start to conduct and thus stops the current going negative. The result of this is that C608 becomes a DC voltage source, which will discharge via the primary winding and C720, i.e. the current will start to increase again until it reaches point t4. This is were there is no energy left in C608 and the primary winding. At this point, 38uS after Q602 has turned off, Q602 will be turned on again and the cycle repeats.

Figure 18 : Line Current and Voltage Waveforms ( Idealised )

Note that as the voltage across the primary winding is proportional to the rate of change of current in it and since the rate of change is constant during the forward scanning stroke, but fast during the flyback period, the voltage across it ( and the scanning coils ) will be a series of pulse. This is also shown in the diagram below.

Also note that the above is an ideal explanation of the circuit operation, the actual waveforms generated will be somewhat different to those shown on the previous page.

#### Line scan correction

L605 provides for line linearity correction and R611 will damp any excessive voltage spikes across it, these spikes may cause striations on the left hand side of the screen if left undamped.

As the tube face is virtually flat, if the scanning current was not modified, this would result in the picture being cramped in the centre and stretched at the sides. To alleviate this it is necessary to compensate for the rate of change of the line scan current, i.e. to slow down the current at the start and end of scan. This can be achieved by fitting the correct value of capacitor in series with the line scanning coils. Normally referred to the S-correction capacitor, this is C613.

East/west correction is provided by the diode modulator and is explained in more detail in the **East/west** correction section of these notes.

#### Sand castle pulse

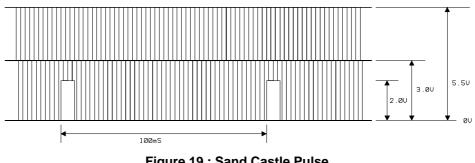

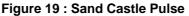

For correct internal processing within IC201, a reference pulse needs to be generated from the line and frame signals. This is referred to as the sand castle pulse and its wave shape is shown in the diagrams below.

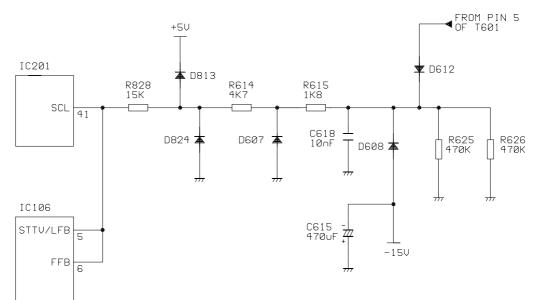

To generate this pulse it is necessary to sample both the line and frame signals. The line pulse comes from the line output transformer, T601, and the frame pulse from the teletext processing IC, IC106. The line pulse generated from the line output transformer is rectified by D612, ensuring that only positive going pulses are present on its cathode. Connected to the cathode of D612 is D608 which is used to reduce the pulse by fifteen volts. This will ensure that the overall level of the line pulse will not exceed 5.5V when it arrives at pin 41 of IC201.

R625 and R626 provide a load for the line pulse and R615 limits the current/voltage supplied. C618 suppresses any high frequency signals that may occur on the line pulse. These would be undesirable as they may cause unpredictable false triggering within IC201. D607 and D824 ensure that no erratic negative going pulses are present on the line signal. D813 ensures that the line pulse is pulled up to the +5V supply when present and to zero when not.

Figure 21 : Sand Castle Pulse Generation Circuit

#### **East/West correction**

#### Principle of circuit operation

If the width of the picture were not varied during the line scanning process, it would result in a picture that would be wide at the top and bottom, but narrow as it progresses towards the centre. This effect is especially noticeable on large CRT's due to the distance the beam has to travel. The circuit used to correct for this distortion is called the east/west correction circuit and is described below.

At the end of line flyback time, the charge on C608 and C610 decays slowly to provide the first half of the scan. When the centre of the scan is reached Q602 will switch on and the scanning coils are supplied with current via the charging action of C613 ( the S correction capacitor ). Therefore, it can be seen that by changing the charge on C610, the width of the picture can be changed.

#### Circuit operation

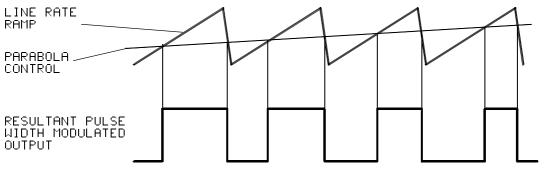

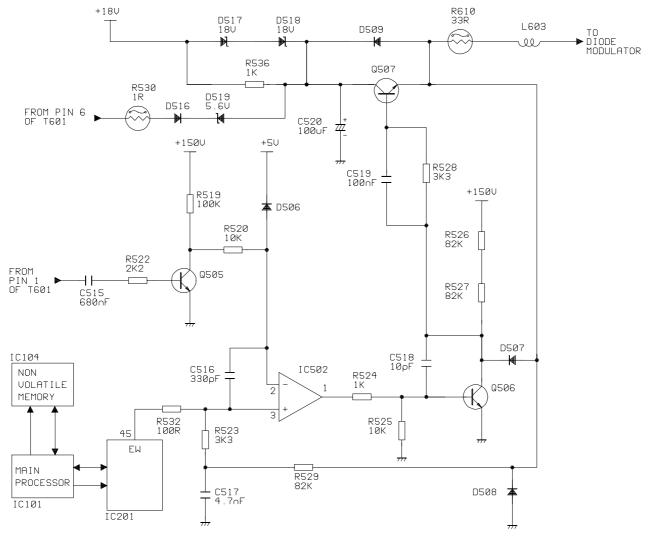

Pin 45 of IC201 provides a parabola waveform at field rate that contains all the correction signals supplied from the NVM for picture geometry. This is added to the negative feedback signal from the output stage and is fed into IC502

IC502 (pins 1, 2 and 3) comprises a pulse width modulator whose non-inverting input, pin 3, determines the width of the pulse. The signal present on the inverting input of the amplifier is a ramp waveform, generated from a line pulse off the line output transformer.

At any instant in time, the voltage on the inverting input of IC502 will directly affect the timing of the signal on the output, i.e. when the ramp waveform crosses the threshold set by the parabola, the output of the amplifier will switch to a high level (see the diagram below). The maximum amplitude of the signal connected to pin 2 (ramp) is three volts and the maximum level of the signal on pin 3 (parabola) is one and a half volts. Therefore when the parabola is at its maximum level, the duty cycle of the output will be 50/50 and when the control voltage is lower the mark will increase to point set by its base line voltage.

#### Pulse width modulator

This ramp waveform is generated by the action of C516 and R519/520 under control of Q505. Initially the base of Q505 will be low and therefore C516 will be allowed to charge via R519 and R520. When Q505 is turned on as its base rises above 0.65V, the charging will stop and the capacitor will discharge via R520 and the collector/emitter junction of the transistor. Because the charge time is approximately eleven times that of the discharge time (R519 + R520 as opposed to just R520), the ramp will be gentle compared with the discharge.

#### **Drive Circuit**

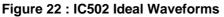

This resultant pulse width modulated waveform is now fed into the base of Q506. The collector of this transistor is taken to the 150V supply via R526 and R527 which allows the voltage at this point to rise to approximately sixty volts. The actual signal generated is a pulse, whose width is dependent upon the on time of the pulse width modulated waveform, but as signal inversion takes place, the on time of the modulating signal will result in the off time of the pulse.

C610 provides the earth return for the line scanning coils, there will also be a pulse waveform at this the

top of this capacitor will be in excess of 160V peak. The start point of the two waveforms on the cathode of D507 (60V peak) and the anode (160V peak) will occur at the same time, but the cathode will turn off sooner (determined by the modulating input signal of Q506). This being the case, the signal on the anode of D507 will be modulated with amplitude variations on each line pulse, and these variations will vary depending upon the point at which they occur in the parabola. The resultant waveform on the top of C610 will be a line pulse signal, modulated with the controlling parabola. This now meets our above criteria of changing the charge on C610 to vary the width of the picture during the frame scan.

#### Figure 23 : Idealised East/west Pulse Waveforms

As the east/west output circuit only requires power during the pulse part of its operation, it is possible to reduce the power dissipated by the circuit by using the circuit based around Q507. At initial start up, no voltage will be present in the east/west output circuit ( because the line has not started up ), so the +18V supply from the chopper stage is used to charge up C520. When the collector of Q506 goes high, it will turn on Q507 so that voltage can be supplied from C520. As the line stage starts up, the charge on C520 needs to be replenished quickly and this is done from the line output transformer itself ( pin 6 ) via D516 and D519. D517 and D518 along with the +18V supply ensure that the voltage on the collector of Q507 does not exceed fifty four volts at any time.

D509 protects the collector emitter junction of Q507 should the pulses on the top of C610 become excessive.

A feed back circuit comprising of D508, R529, C517 and R523 provides negative feed back from the output of the driver stage. This is to prevent the circuit from oscillating, drawing too much current and causing damage to Q506 and Q507.

Figure 24 : Diode Modulator Circuit

The obvious advantage of this circuit configuration is that Q506 and Q507 are only conducting during the active line scanning period. This coupled with the fact that they are used as switches, i.e. maximum current/no voltage or no current/maximum voltage means that there is very little energy generated within these devices. Thus power consumption is kept down to a minimum.

Note that the east/west adjustment is made in the service mode and is referred to in the **Service set up mode** section of these notes.

Figure 25 : East/West Drive Circuit

#### Supplies generated by the line stage

•

A number of conventional supplies are generated from the line output transformer, EHT, Focus, G2, A1 and CRT heaters. A further +/- 15V is also generated for the vertical output stage. Also there is a +2V supply for the east/west diode modulator and a -10V supply which along with the +2V supply is used to drive the line output transistor. See the **Line drive circuit description** section of these notes for more details on this.

i.

i.

| Supply Name | Voltage ( approx ) | Purpose                             | Point of Generation      |

|-------------|--------------------|-------------------------------------|--------------------------|

| EHT         | 28kV               | CRT final anode                     | Top of split diode chain |

| Focus       | 8kV                | CRT focus grid                      | Split diode chain        |

| G2          | 500V               | CRT grid                            | Split diode chain        |

| CRT Heaters | 3VAC               | CRT Heaters                         | Pin 1 of T601            |

| +45V        | +45V               | East/west correction circuit supply | D510, Pin 6 of T601      |

| +45V        | +2.0V              | Line drive                          | D605, Pin 10 of T601     |

| +15V        | +15V               | Vertical output supply              | D609, Pin 9 of T601      |

| -15V        | -15V               | Vertical output supply              | D608, Pin 5 of T601      |

| -45V        | -10V               | Line drive                          | D602, Pin 6 of T601      |

As the +/-15V supplies are generated by the line stage, there will be no vertical scanning or sound output until these have come up (note that the sound output stage is supplied from the chopper +/-18V supplies, but no current will be supplied until it starts to amplify the output from IC305, this is muted until the line stage is fully functional ). Also the +45V supply will not be established until the line stage is running. This effectively ensures that the line stage 'soft starts' and therefore significantly reduces the risk of component failure as the receiver is turned on, i.e. current is taken from the chopper supply in the following time sequence :-

- 1. Line stage starts up at 31.25kHz using the -18V and +13V supplies from the chopper.

- 2. Feed back is received from the line stage and IC201 switches to 15.625kHz.

- 3. Line stage runs (+150V from the chopper and -10V/2.0V from line stage).

- 4. Vertical stage starts up using the +/-15V supplies from the line stage.

- 5. Current is drawn for the sound output stages as the output from IC305 is turned on.

- 6. RGB drive is turned on and current is drawn from the +150V supply from the chopper by the CRT drive IC.

Note that the CRT drive amplifier is not supplied from the line output stage, as in other Sharp television chassis, but is derived direct from the 150V supply generated by the chopper stage.

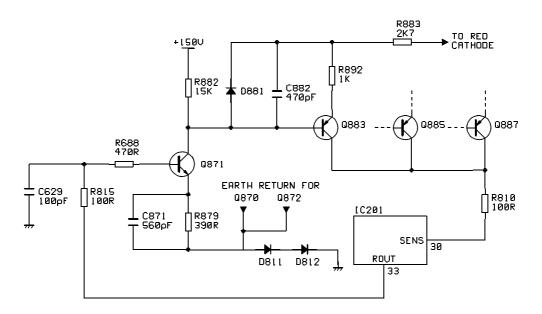

#### **Beam current limiter**

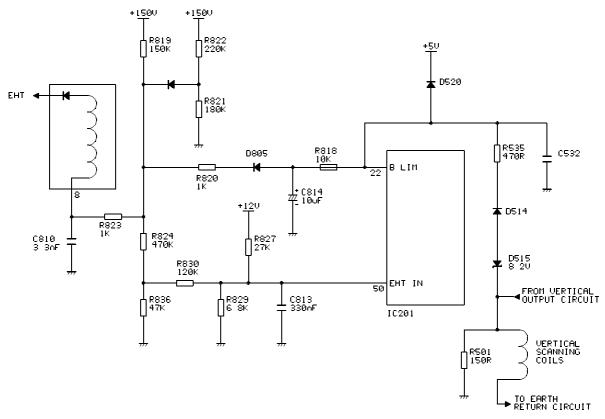

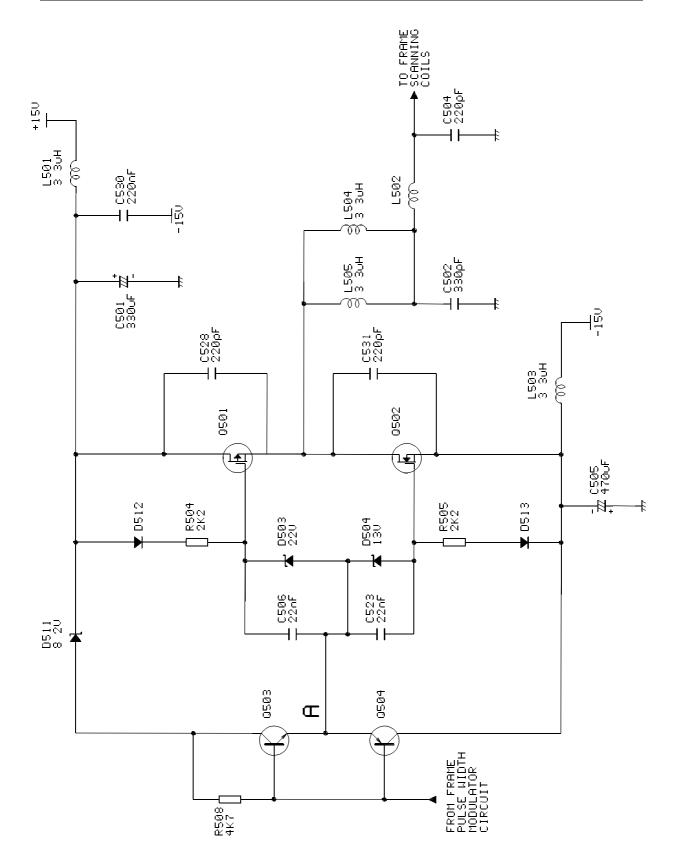

Beam current limiting is carried out to remove the risk of forward X-ray emissions, to stabilise the EHT and control picture brightness. Feedback to control the beam current is taken from the bottom end of the EHT over winding as shown in the diagram below.

Figure 26 : Beam Current Limiter Circuit

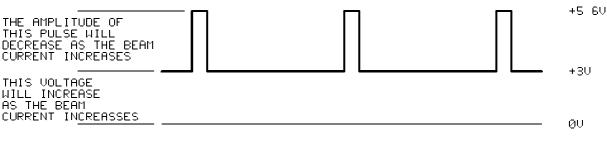

Feed back for the beam current limiter is taken from the bottom end of the EHT over winding on pin 8 of T601. This produces a DC voltage which is fed into pins 22 (B LIM) and 50 (EHT IN) of IC201. When the beam current increases, the voltage on pin 8 of T601 will rise, conversely as the beam current decreases the voltage on this pin drops.

Beam limiting input of IC201

Pin 22 ( B LIM ) will ensure that the picture brightness is maintained within limits should the beam current increase or decrease by varying the amplitude of the video signal. Should the beam current become excessive, then IC201 will reduce the amplitude of the video signal so that the screen blanks out ( raster still present, but no picture ). If the beam current then increases still further, the video signal will be reduced below the black level to give an ultra black picture.

The signal on pin 22 is a pulse ( at vertical rate ) sitting on a DC pedestal of three volts ( nominal value as this varies anywhere between +1V and +4V).

Vertical circuit failure - CRT protection

If the vertical drive were to stop, a bright white vertical line will appear across the centre of the CRT. This is obviously undesirable as it may burn the phosphor coating if left on for too long. To alleviate this possibility a feed is taken from the vertical output ( top end of the vertical scanning coils ) via D515. D515 ensures that only signals greater than 8.2V pass to pin 22. D514 provides isolation and D520 clamps pulse to a maximum level of five volts.

Under normal conditions this has no effect on the operation of the beam current limiter. When the vertical drive signal falls below 8.2V (flyback pulse) the pulses developed at the cathode of D514 will disappear and this will cause the screen to go ultra black, ensuring that no damage is done to the CRT. In this situation, if the beam current is increased by turning up the G2 control on T601, a thin horizontal white line will be seen momentarily unit the beam current limiter circuit compensates and turns the current down again.

#### EHT input of IC201

If the beam current increases significantly, then there will be a risk of forward X rays being generated from the CRT face. To prevent this condition, pin 50 (EHT IN) is used to monitor for excessive beam current.

Although the B LIM pin will reduce the risk of forward emissions, as it only changes the video signal, the EHT IN pin will override this operation. When active, i.e. X ray emission may be possible, pin 50 will return the set to standby. This pin is nominally 2VDC, but this will change slightly with beam current.

## Vertical Stage

#### Vertical time base generation

A R/C oscillator within IC201 provides a vertical drive signal for the vertical drive and output stages . External components are used to control the stability and phasing of this signal ( note that the external crystal is not used as a reference source - the vertical stage will operate with this component disconnected from the circuit ) When a video signal is present, this oscillator is locked to the incoming vertical synchronisation pulse.

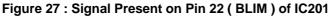

Figure 28 : Vertical Stage Block Diagram

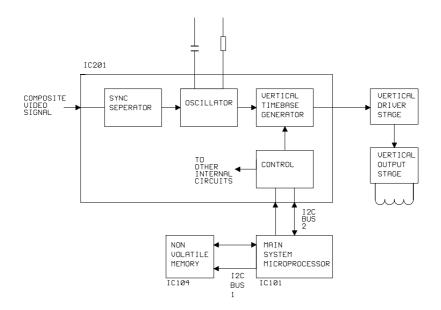

The oscillator has two outputs that exit IC201 from pins 46 (V OUT P) and 47 (V OUT N). Pin 47 provides the main drive signal, while pin 46 provides the correction signal, i.e. the vertical geometry signal. The geometry settings are contained within the non volatile memory and are accessed via the  $I^2C$  bus and the microprocessor.

As can be seen from the diagram on the next page, the vertical drive signals from IC201 pass into the operation amplifier IC502 on pins 5 and 6. This amplifier sums the two inputs, the resultant output being fed into pin 6 of IC501. Feed back from the vertical stage comes from the bottom end of the vertical scanning coils via R516 and R539. This is to ensure that the vertical stage does not drive the coils incorrectly due to inefficiencies within the vertical drive or output circuits, i.e. it provides negative feed back. Also connected to this feed back point is the output from pin 47 of IC201, this pin is effectively the frame correction signal.

The input to the second operational amplifier, IC501, is also affected by the vertical scanning coils drive signal (top end of the vertical scanning coils). This enters via R511 (to the inverting input on pin 6) and R509 (to the non-inverting input on pin 5). This provides positive feed back and therefore will cause the stage to oscillate. This oscillation is free running, but remains at about 140kHz (this is set mainly by C509 and R509). The output from pin 7 is a square wave whose frequency and mark/space ratio is dependant upon a number of factors. One is the drive signal itself, two the frame geometry settings and three the frequency of oscillation generated by the feedback to IC501. This signal then drives Q503 and Q504 in the frame drive circuit described in the next section.

Both IC501 and IC502 are supplied on pin 8, +5V and 4, -15V. This ensures that the output from pin 7 of IC501 is swinging both positive and negative.

Vertical geometry is set using the software service mode and therefore all adjustments are stored in the NVM, IC104. Please refer to the **Service Set Up Mode** section of these notes for information on how to set the geometry of the vertical stage output.

Figure 29 : Vertical Drive Circuit

Vertical scan coil drive circuit

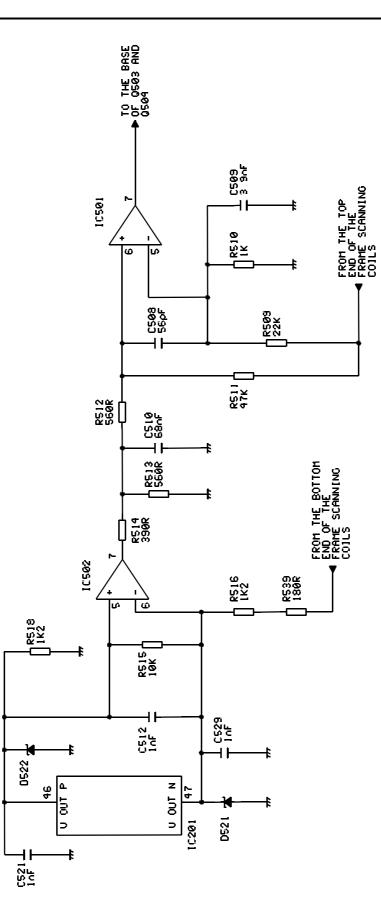

The vertical output stage used in the CA10 chassis is based around two field effect transistors - Q501 and Q502. As power consumption and therefore heat generation needs to be kept to a minimum a class D amplifier type configuration is utilised. This basically means that the FET's are used as switches to switch either the +15V or -15V into the output load ( in this case a low pass filter ) then into the vertical scanning coils. This is based upon the fact that the input signal from the drive amplifier is a pulse width modulated signal whose base frequency is 140kHz.

Transistors Q503 and Q504 ensure that the drive signal present at the junction of Q503 emitter and the collector of Q501 (marked as point A in the circuit diagram on the next page), swings between -14.4V and +4.4V. When the drive signal is high (positive), Q503 will be turned on and point A will be +4.4V. When the drive signal is low (negative) then Q504 will turn on and point A will be -14.4V. This is necessary to ensure that the output FET's are operating in their fully saturated states, if they were not fully saturated then the circuit would become inefficient and heat would be generated eventually resulting in the failure of the FET's.

Note that D511 ensures that the voltage on the collector ofQ505 does not exceed 6.8V as any voltage greater than this will damage the device. Q503 and Q504 are emitter followers and as such their emitters will follow the base voltage, therefore if there is too large a volt drop across the collector/emitter junctions of these transistors they will fail.

When point A is at +4.4V, the zener diode D504 will be forward biased and therefore current will flow from the -15V supply via D513 and R505. The gate of Q502 will rise to -6.8V and turn it on and effectively connect the -15V supply to the output load. At this time the other FET, Q501 will be turned off as its gate will be +15V by the pull up action of R504 and D512 (D503 is not conducting).

When point A changes to -14.4V, Q502 will turn off as D504 ceases to conduct and its gate voltage will drop to -14.4V by the action of the pull down of R505 and D513. At the same time, D503 will become forward biased resulting in a voltage of +7.6V on the gate of Q501 which is enough to turn it on and connecting the +15V supply into the load.

It is vitally important that both Q501 and Q502 are not turned on at the same time as excessive current will flow between the positive and negative fifteen volt lines resulting in the FET's going short circuit and the supply feeds going open circuit. To ensure that this does not occur, each FET needs to be held off momentarily until the other one has stopped conducting. This is achieved by the capacitors connected across D503 and D504.

When Q501 is conducting, the voltage on the gate of Q502 will be held at -15V, keeping it turned off. As the polarity of point A changes and Q501 is turned off, C523 will retain enough charge to hold the gate of Q502 at -14.4V until Q501 is turned fully off. The reverse occurs when Q502 turns off, but this time capacitor C506 is used to keep Q501 off. This happens as it takes a small amount of time to charge each capacitor during the cycle, therefore if the value of the capacitor goes down, or one goes open circuit, the FET's would over heat or in worst case expire. By holding off the conduction of Q501 and Q502 momentarily cross over distortion will occur. In a conventional amplifier this is undesirable as it will cause distortion in the output signal. However, as the output signal passed through a low pass filter to recover the original frame scanning signal, this cross over distortion can be ignored, i.e. it has no effect on the drive signal.

From the source of Q502/drain of Q501 the amplified pulse width modulated drive signal passes into a low pass filter comprising of L504, L505, C502, L502 and C504. This has the effect of removing the oscillation of 140kHz and leaves the vertical drive signal at 50Hz. This voltage is now fed into the vertical scanning coils via the socket assembly.

Note that as the positive and negative fifteen volt supplies are generated by the line stage, there will be no frame scan until the line stage has come up.

Figure 30 : Vertical Output Stage

## **Tuner and IF**

Tuning and IF control is provided by the system microprocessor, IC 101 via the  $I^2C$  bus line. The tuner itself is a digitally controlled device, which eliminates the need for a separate VT line generator circuit. As the tuner is controlled directly from the microprocessor, it is easier to provide direct channel entry and as an added feature the set is also equipped with auto channel sorting. This is across the normal UK channel band and cable channels.

Most of the IF circuitry is contained within IC201 (Video IF) and IC305 (Audio IF), the minimal amount of external components provide for IF signal filtering - see **IF signals** section for more details.

#### Tuner and IF processing

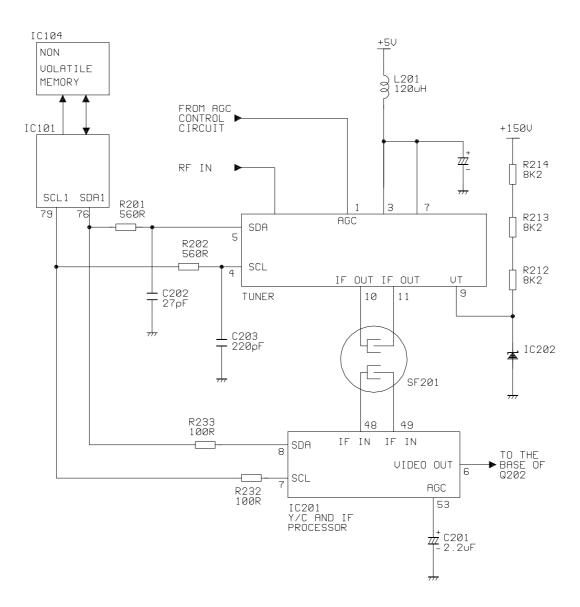

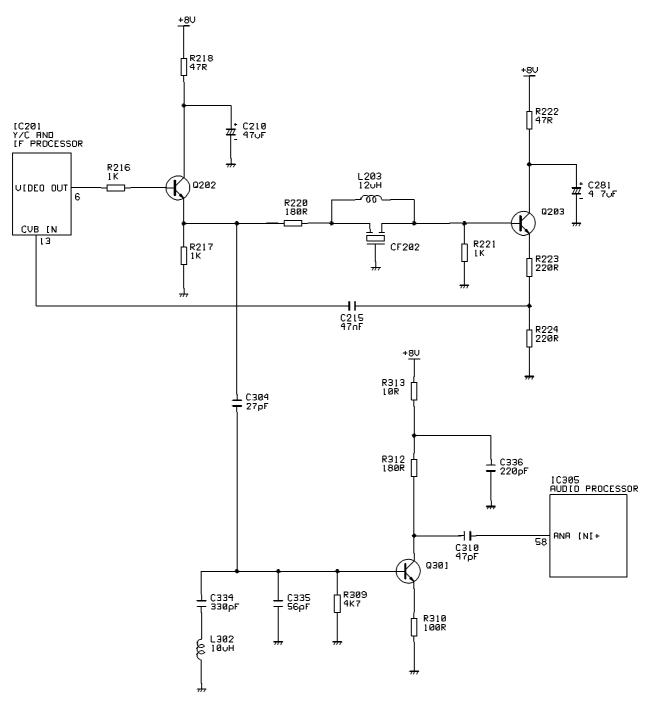

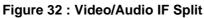

All IF processing is carried out within either IC201 for video or IC305 for audio. Initially the IF from the tuner enters IC201 and is decoded to produce the base band signal - see the spectrum diagram shown later in these notes. As this is a composite of the video and audio IF (FM and NICAM) signals it is necessary to process it further to ensure that no corruption occurs in the later stages. The circuit shown below serves this function.

#### Figure 31 : Tuner and IF Signal Path

When the user selects an off air signal, data is taken from the NVM and used by the microprocessor to generates the data signal fed into the tuner. This data will control the digital to analogue converter contained within the tuner module so that the correct voltage is applied to the varicap diodes. Like most tuners it is necessary to provide a 32 volt supply line to allow for total band coverage of the tuning voltage,

this is provided from the +150 volt line via the dropper resistors R211, R213 and R214 and IC202. IC202 is effectively a 32 volt high stability zener diode.

Other supplies need to be present to make the tuner work correctly. Although there is only one other supply source (+5V) this is used internally for the digital to analogue converter, RF amplifier, tuning stages and IF processing circuits. The low pass filtering circuit on the supply line comprising of L201 and C204 ensure that no high frequency noise enters the tuner, this could lead to the tuner oscillating erratically resulting in picture corruption.

Once the tuner has tuned into a channel, the IF signal output passes out of pins 10 and 11 via the SAWF filter, SF201, and into the main IF amplifier contained within IC201. IC201 then further amplifies the signal and converts it into a composite baseband signal.

#### Automatic frequency control

To keep the station on tune at all times, an automatic frequency control system is utilised. Once again this circuit is based around the system microprocessor. Unlike previous chassis, there is no external AFC circuitry, as all the processing is done within IC101 and IC201. If it is seen the signal is going off tune, then the microprocessor will change the RF tuning point within the tuner via the  $I^2C$  bus line. The reference for the AFC circuit is maintained by the detector coil T201, which has to be correctly set to ensure that the set does not drift off tune on off air broadcasts.

#### Tuning features

As this receiver uses a digitally controlled tuner, it is possible to add some advanced user features to the receiver. Direct channel entry is possible using the remote control and auto sort tuning is provided.

As the receiver leaves the factory, the auto sort tuning feature is enabled, this is so that the end user does not have to manually tune the unit in when getting it home. When the receiver is first turned on, the end user is presented with a screen that instructs them to connect the aerial, VCR (while playing a tape) and satellite receiver (switched on and tuned to a station) to the rear of the set via the RF socket. They are then requested to press any button on the remote control, the auto tuning/sorting sequence will now be initiated.

First the signal carrier is detected, then the sync detector detects a line sync signal and the tuning operation slows down and the signal is fine tuned, both of these operations are contained within IC201 and control is maintained by IC101 via the  $I^2C$  bus 2. Next the teletext header is decoded by IC106 and the time taken to decode it is stored within the NVM, IC104, via the  $I^2C$  bus 1. The data value relating to the VT line voltage is also stored. This process continues for all channels.

When this process is completed the text header ( if transmitted ), time taken to obtain the text header and tuning point will all be stored in the NVM. The set will now sort this information depending on the text header and time taken to obtain the text header. Contained within the EPROM, IC105 is the instructions to store BBC1 on PR1, BBC2 on PR2, ITV on PR3, Channel 4 or SC4 on PR4 and Channel 5 ( if being transmitted ) on PR5. As the VCR was playing a tape ( no text header ) this will be put on CH6 and any other equipment connected at RF will be put on the next available program numbers.

As the receiver may pick up signals from other transmitters, it is necessary for the system processor to decide which ones are more desirable to put in the first positions. This is done by examining the time to decode up the text header. The faster the text header is decoded, the stronger the signal and so the strongest broadcast is stored in the primary position for that station. As it is possible that the incorrect station may be stored in the primary position, i.e. Carlton ITV instead of Meridian ITV, a tuning editing menu is provided so that the end user can change this.

Note that any stations that are too weak to be stored in the primary positions are stored in the remaining free locations after the VCR and satellite channels ( if connected ). For a circuit description of this process, please refer to the **Automatic tuning circuit operation** section of these notes.

#### IF signals

From pin 6 of IC201, the base band signal ( a frequency spectrum of the base band signal is shown on the next page ) passes into the emitter follower, Q202. This ensures that the signal is matched to the following stages and allows buffering from the output of IC201. From the emitter of Q202, the signal splits

into two paths. The first path goes into the base of Q203 via the a 6MHz filter CF202 which removes the audio IF signals from the composite video signal, the second path is via C304 and the high pass filter C334, L302, C335 and R309 into the base of Q301 which removes the video signal from the audio IF signal.

Figure 33 : Spectrum of the Base Band Signal

Each signal path from IC201, pin 6 will now explained in more detail below.

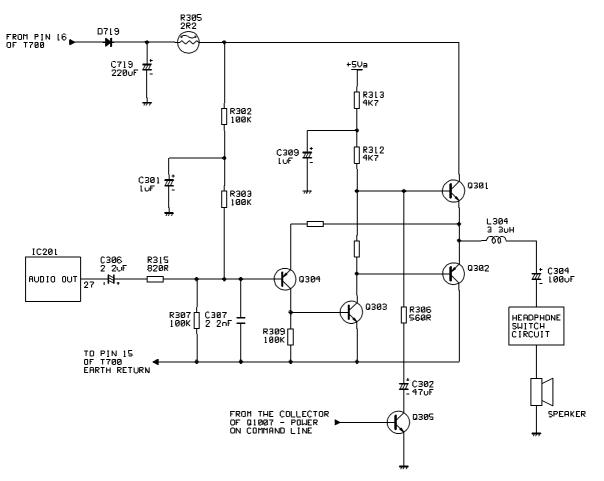

Audio IF processing

C304, being of a very small capacitance, will only pass relatively high frequencies which will effectively remove any signals below about 5MHz. This coupled with the filtering network of C334, L302, C355 and R309 (effectively a high pass filter) will ensure that only the audio FM carrier at 6MHz and the NICAM carrier at 6.522MHz pass into the base of Q301. Q301 amplifies the resultant audio IF and this signal is then coupled via C310 into the audio processor, IC305, at pin 58 (ANA INI+). C336 ensures that no IF signal passes onto the supply.

IC305 contains further IF amplification and the decoder stages to recover both the mono FM and stereo NICAM signals. Switching is carried out automatically within the IC. The receiver will automatically default to the stereo (NICAM) signal, but this can be over ridden by the end user by the use of a menu option. Note that when in the stereo mode, SRS and Dolby can be used, but in the mono mode only stereo wide is available.

For details on the audio switching circuits, please refer to the Audio Processing section of these notes.

Video IF and signal processing

All the video IF circuitry is contained within IC201, the output on pin 6 (VIDEO OUT) is a base band signal as shown in the above diagram.

From the emitter of Q202, the base band signal is passed through CF202 and L203. These components effectively comprise a 6MHz trap and will remove any signals in the audio IF range (FM and NICAM sound carriers), thus the signal entering the base of Q203 will be the video signal. R220/R217 and R221 ensure that correct impedance matching is provided to CF202.

Q202 is an emitter follower which gives the correct impedance match and drive signal back to the video processing circuits contained within IC201. C281 ensures that no video signal appears on the supply line.

From pin 13 ( CVB IN ) of IC201, the video signal is decoded and passes out of the IC as an RGB signal to drive the CRT via IC901.

#### **RF AGC operation**

As signals received from off air transmissions can vary tremendously from area to area, it is necessary to provide some form of automatic gain control on the incoming RF signal. The circuit shown below performs this action.

Figure 34 : Automatic Gain Control Circuit

It can be seen the at the heart of the system is the main system microprocessor, IC101. Via the clock and data lines, IC101 will instruct the tuner to tune to the desired signal ( the data for this operation would have been set by the user at the initial installation and the control values held within the non volatile memory, IC104). The signal from the tuner will enter IC201 ( video IF ) in which there is a detection circuit which will give out a DC voltage on pin 54 ( AGC OUT ) that is dependant upon signal strength. This is fed straight back into the tuner AGC pin which will first control the gain of the RF stages within and then the IF stages, i.e. maximum gain is always given to the RF amplifier to reduce noise.

#### Automatic tuning operation

During the automatic tuning function it is necessary to detect the presence of a signal. While this is done by detecting the presence of a valid carrier signal, it is also necessary to monitor the amplitude of the RF signal to ensure that the RF signal can be correctly decoded. This is one of the functions of the circuit based around one half of IC501.