# F 19 SERVICE MANUAL

THIS DOCUMENT IS A PROPERTY

OF INDUSTRIE FORMENTI ITALIA

NO AUTHORIZED MODIFICATIONS

ARE PERMITTED.

CREATED BY E.G.

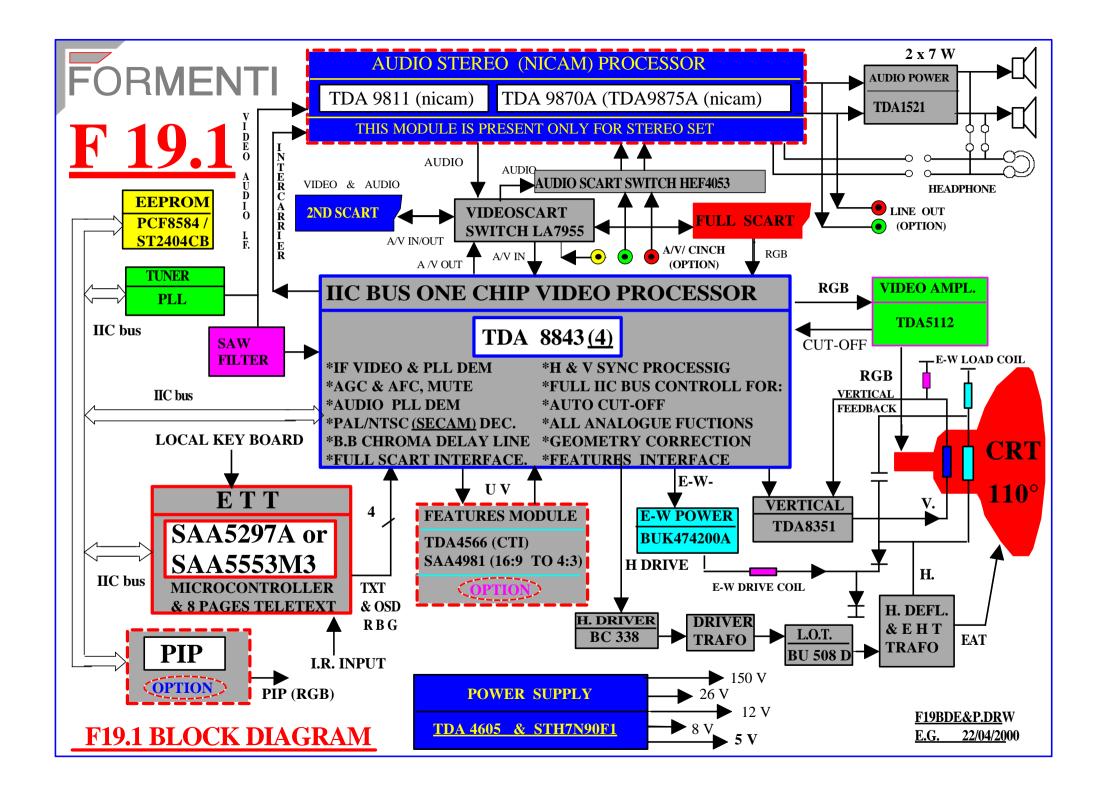

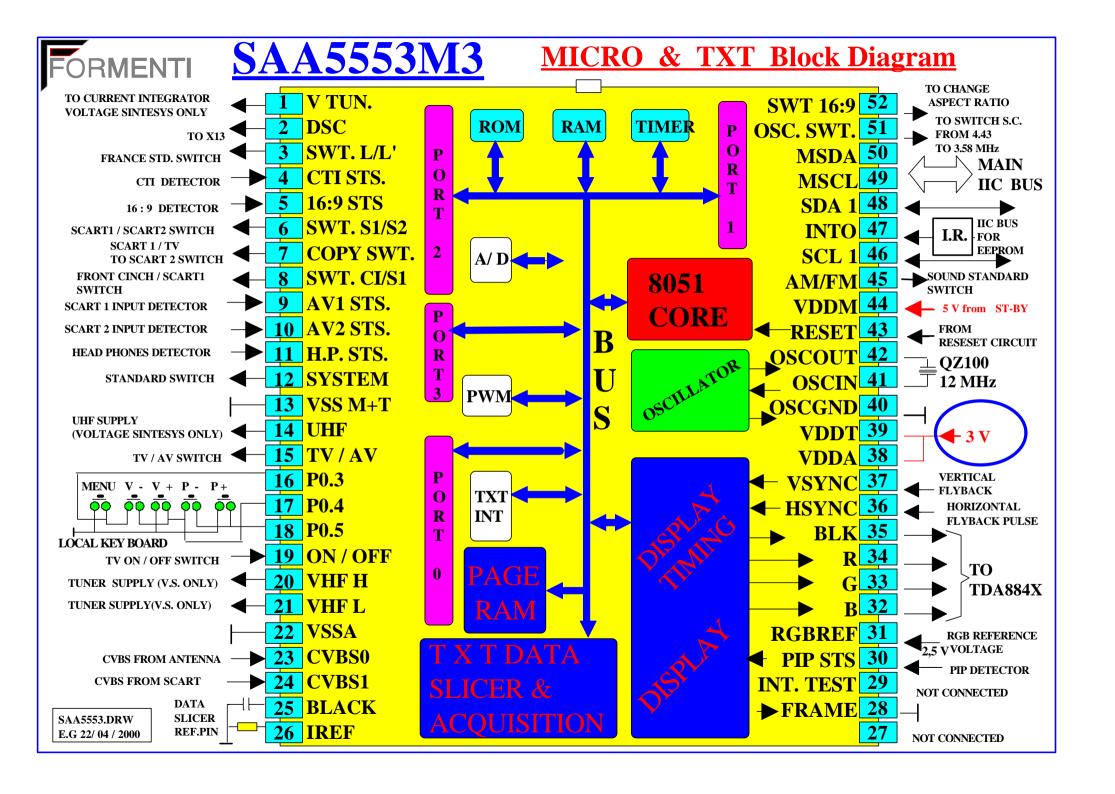

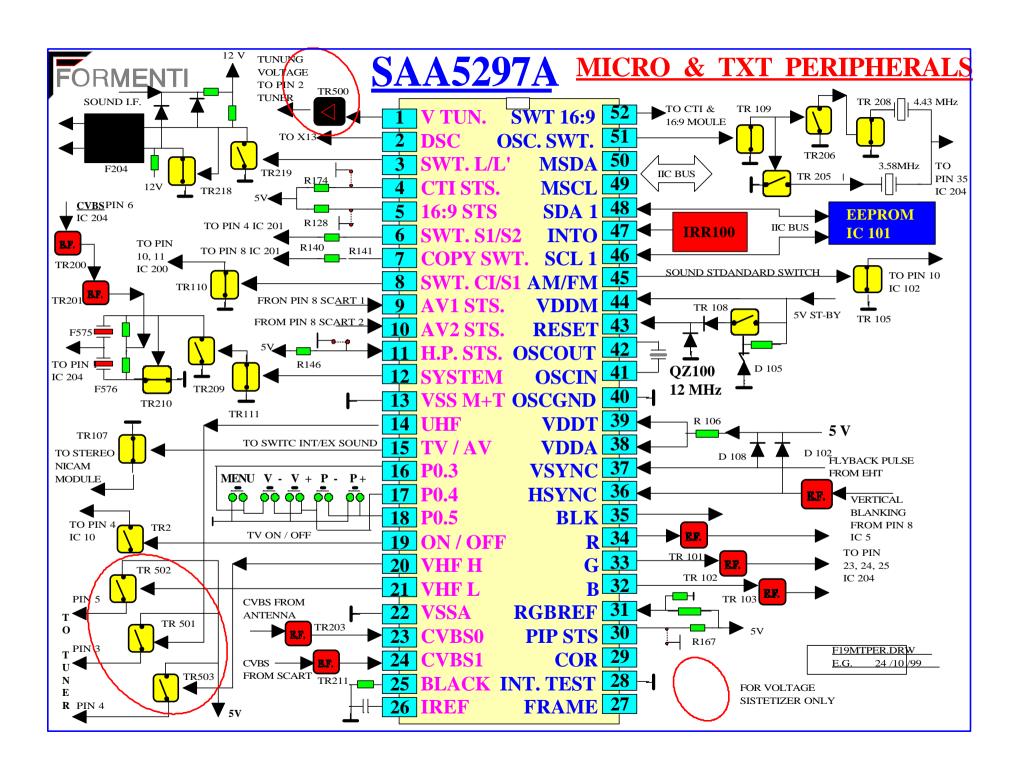

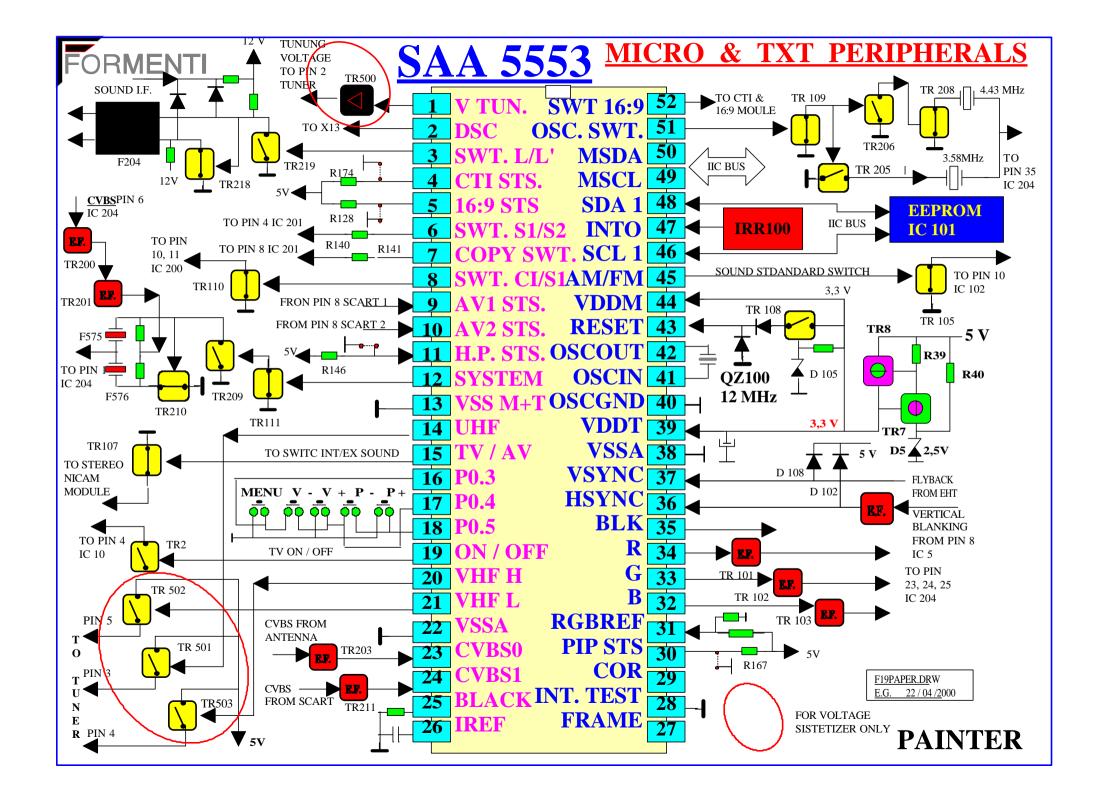

There are two different types of **F19** chassis that are equipped with two different microcontroller.

These microcontroller are known as ETT having a code SAA5297A and PAINTER with a code number SAA5553.

From the point of view of the application on the F19 chassis the two type of microcontroller are substantially having the same performances, the same pinout, the same firmware <u>but they are not interchangeable</u> as the power supply are different.

In case of SAA5297A the power supply is 5 V for the SAA5553 is 3.3 V.

# Even if the two devices are non interchangeable the two chassis can be interchanged as the in/out interface are exactly the same.

As the specifications of the two devices are the same and the first version of the chassis was equipped with the SAA5297A, in this document the characteristics of it are very much detailed meanwhile there is a very short description (as an addendum at the end) for the SAA5553.

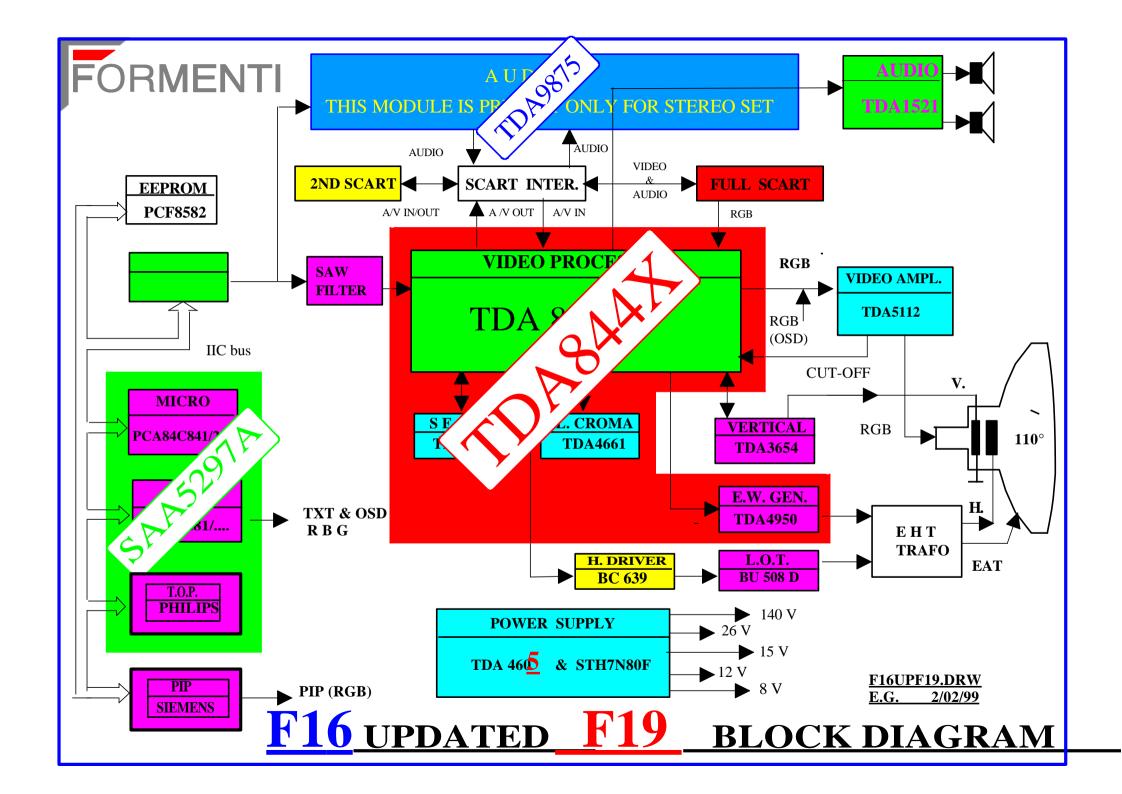

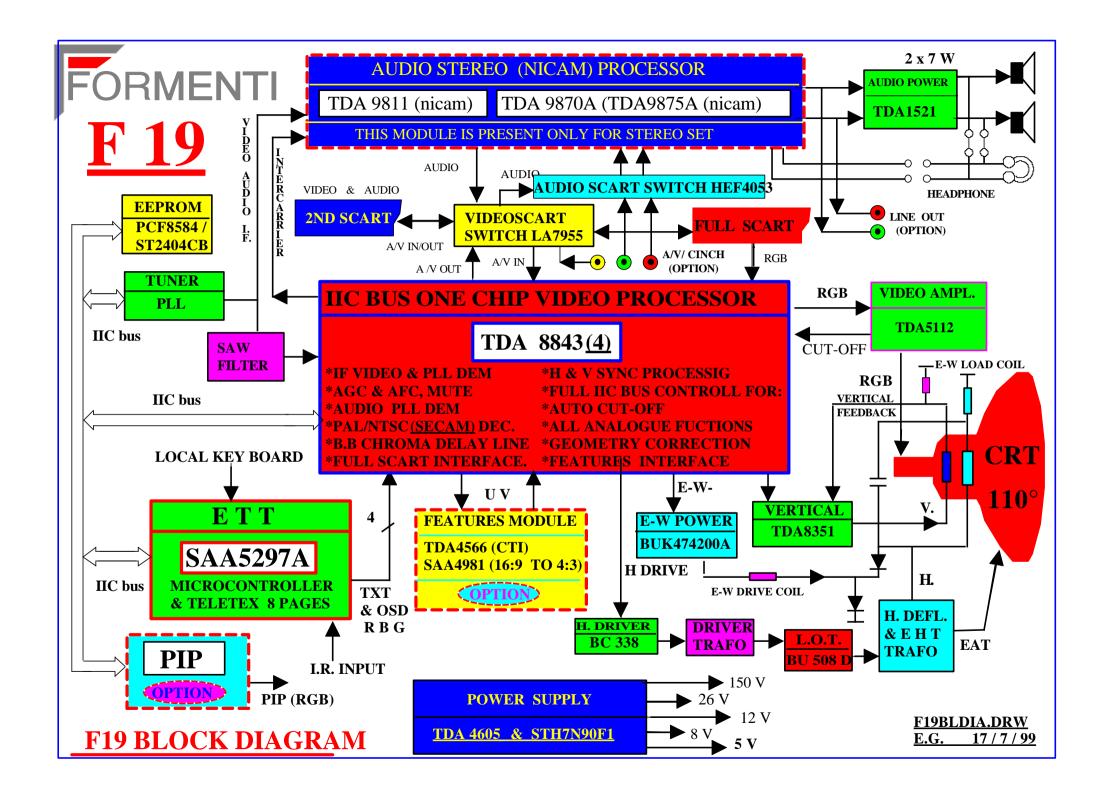

### F19 CHASSIS DESCRIPTION

#### **Summary**

The **F19** is a chassis suitable to drive CRT having both 4 by 3 and 16 to 9 aspect ratio and dimension from 25" up to 34".

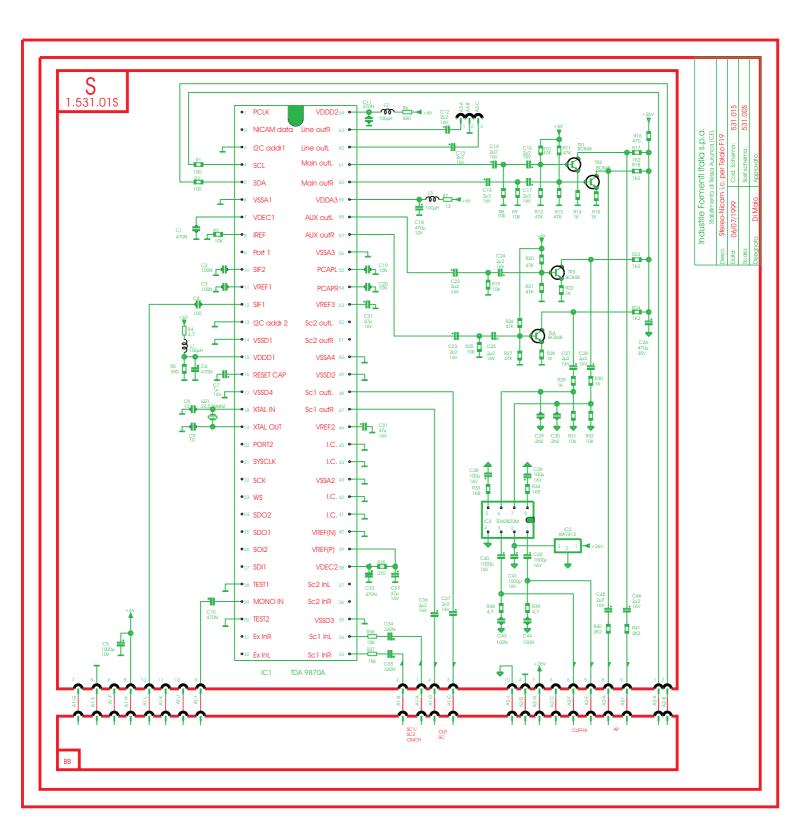

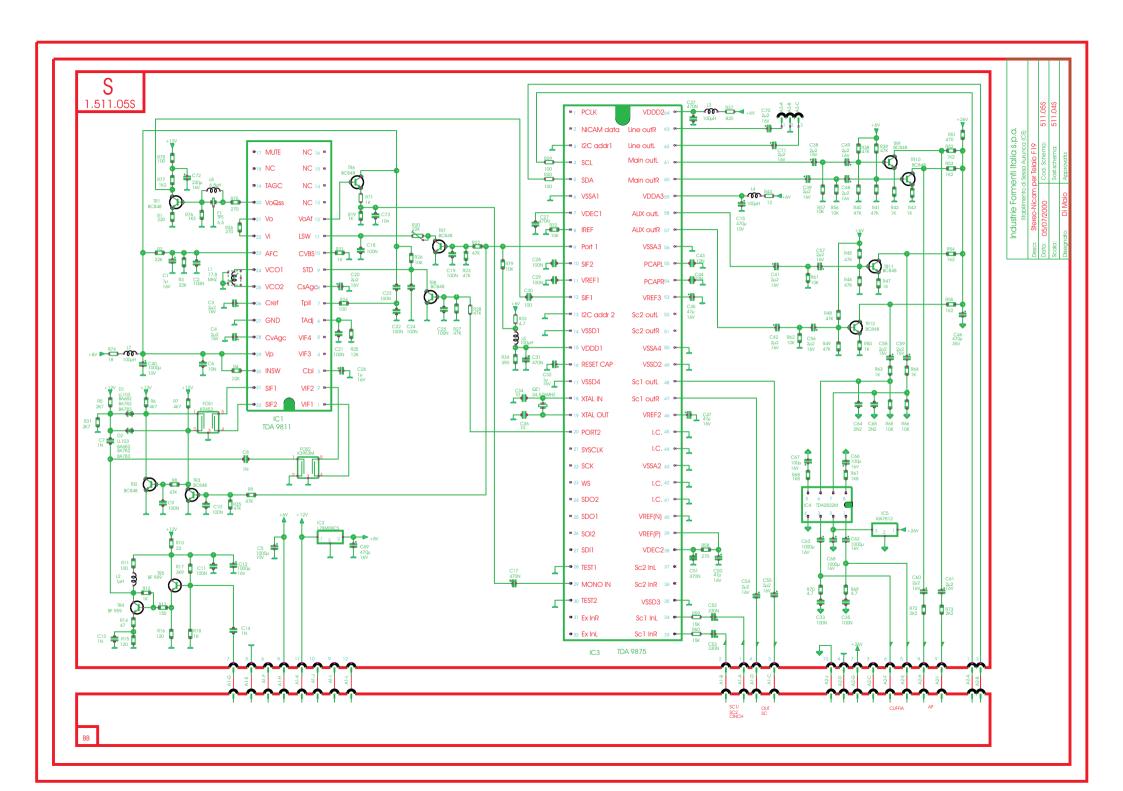

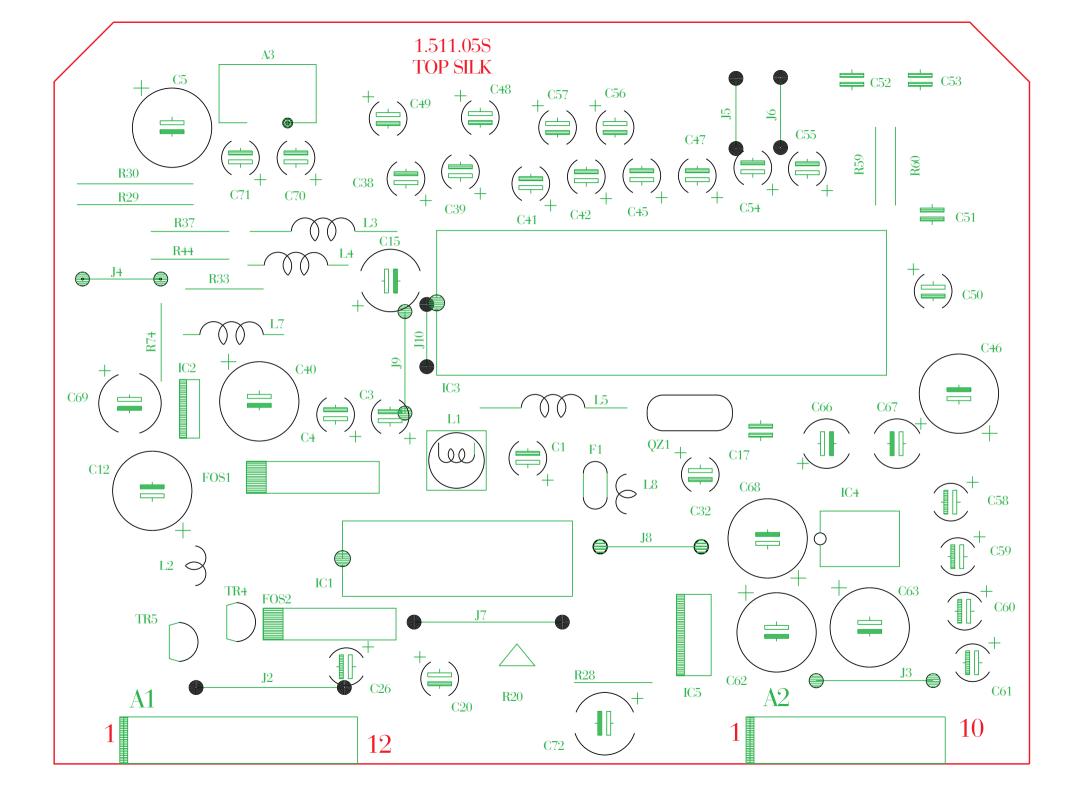

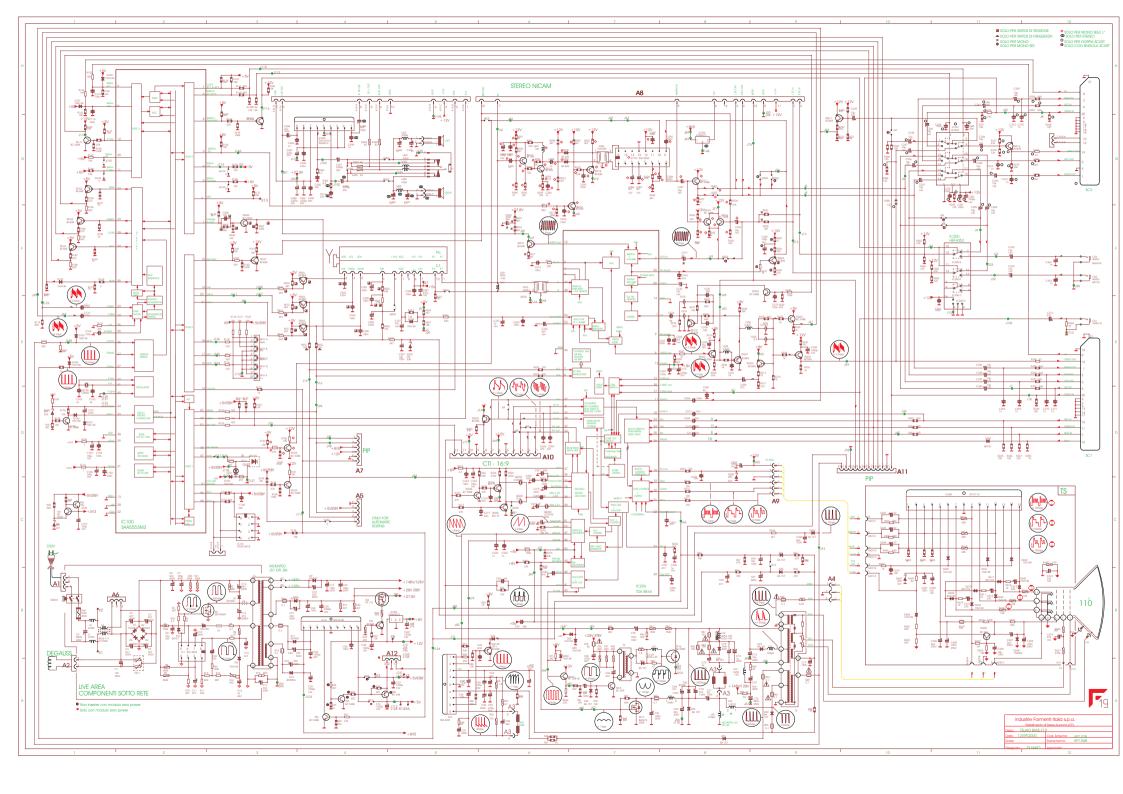

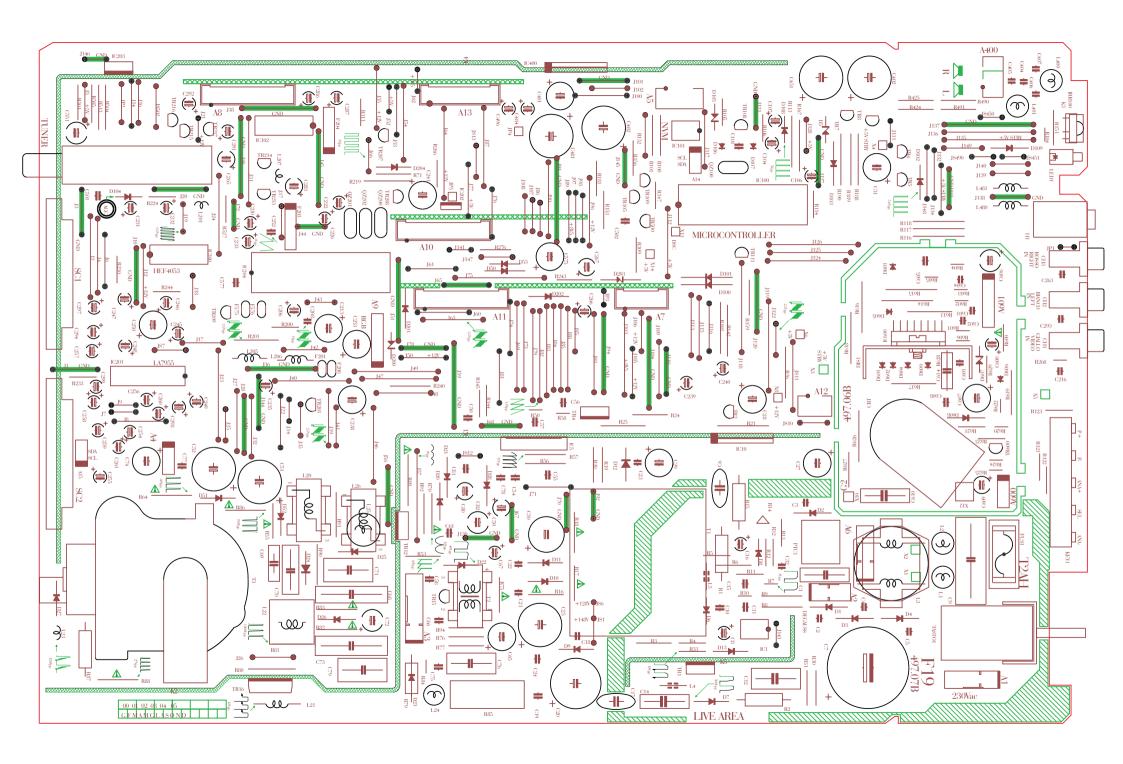

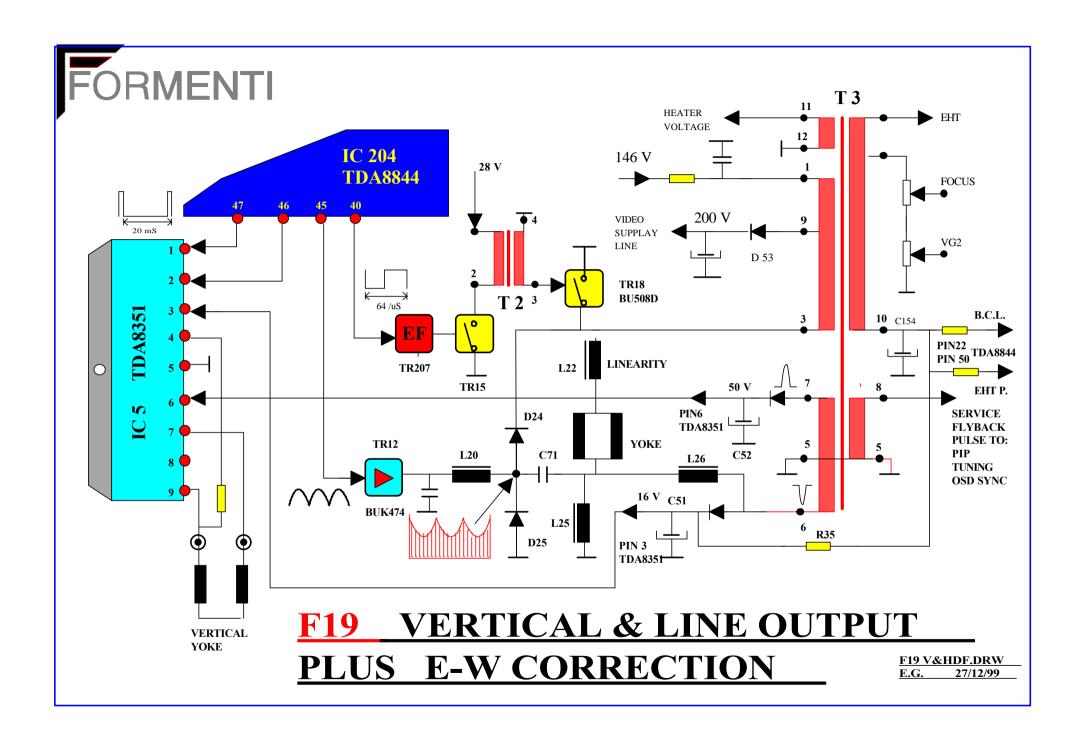

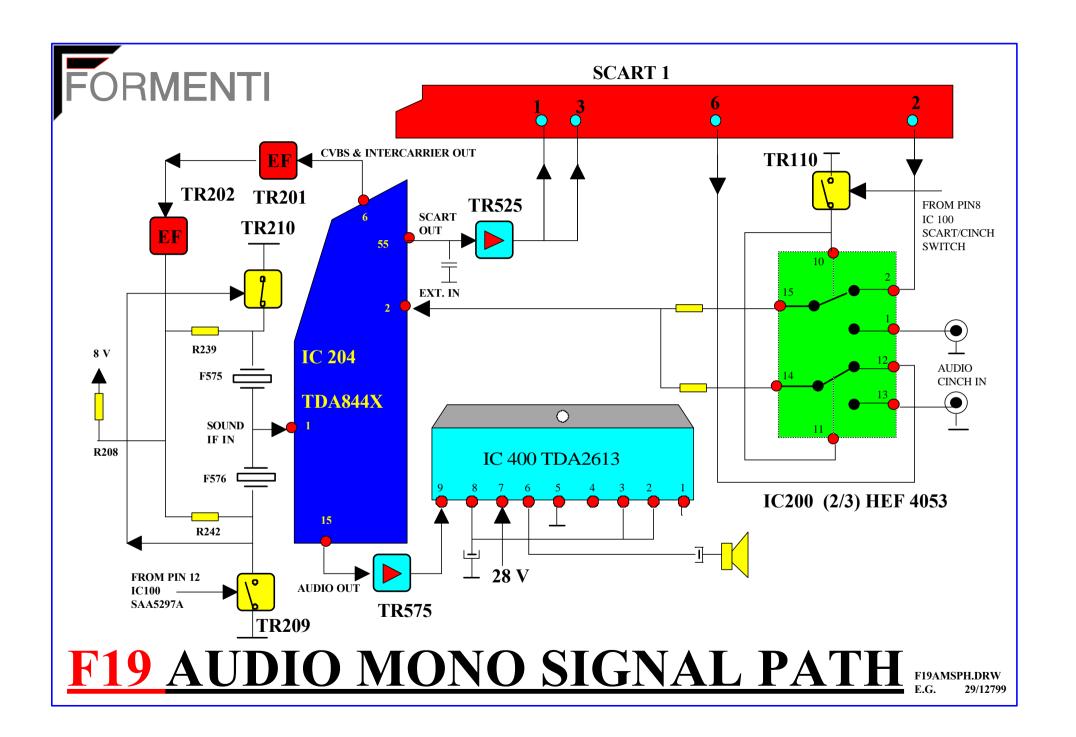

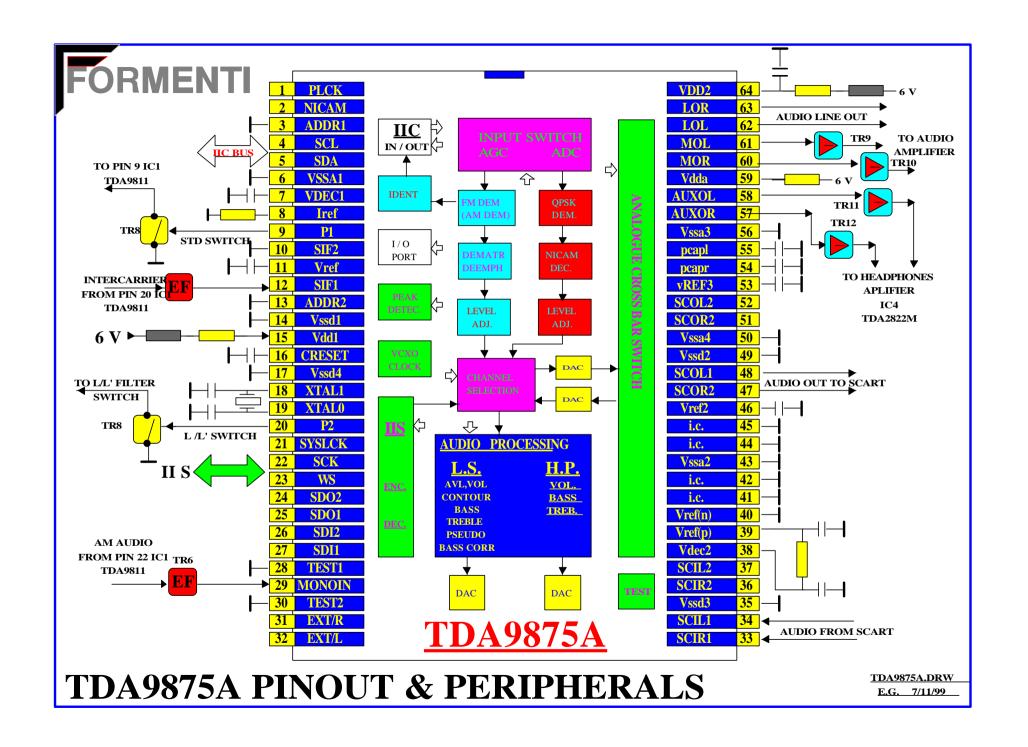

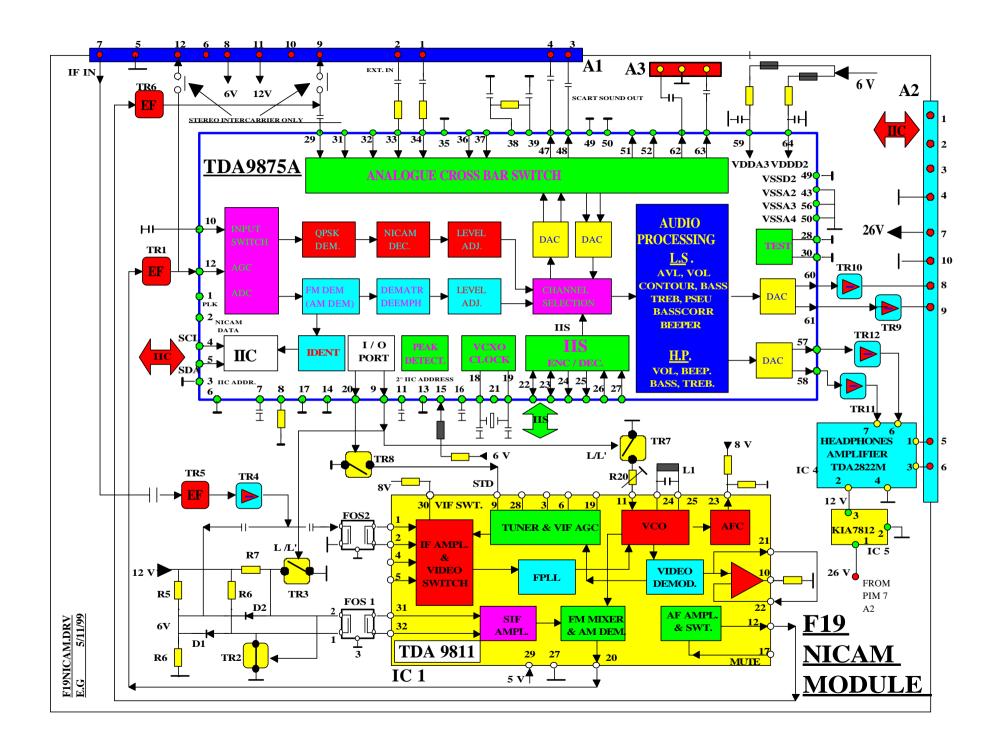

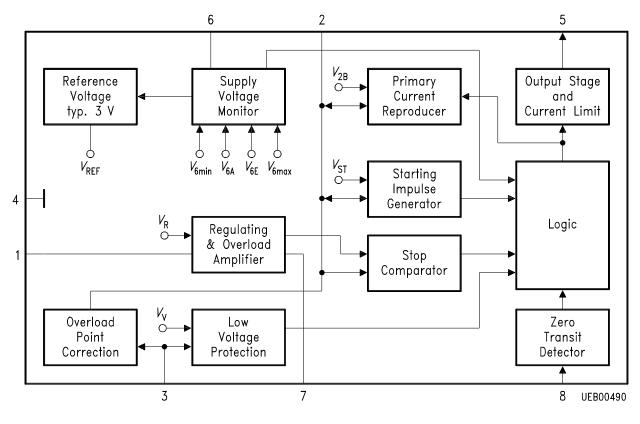

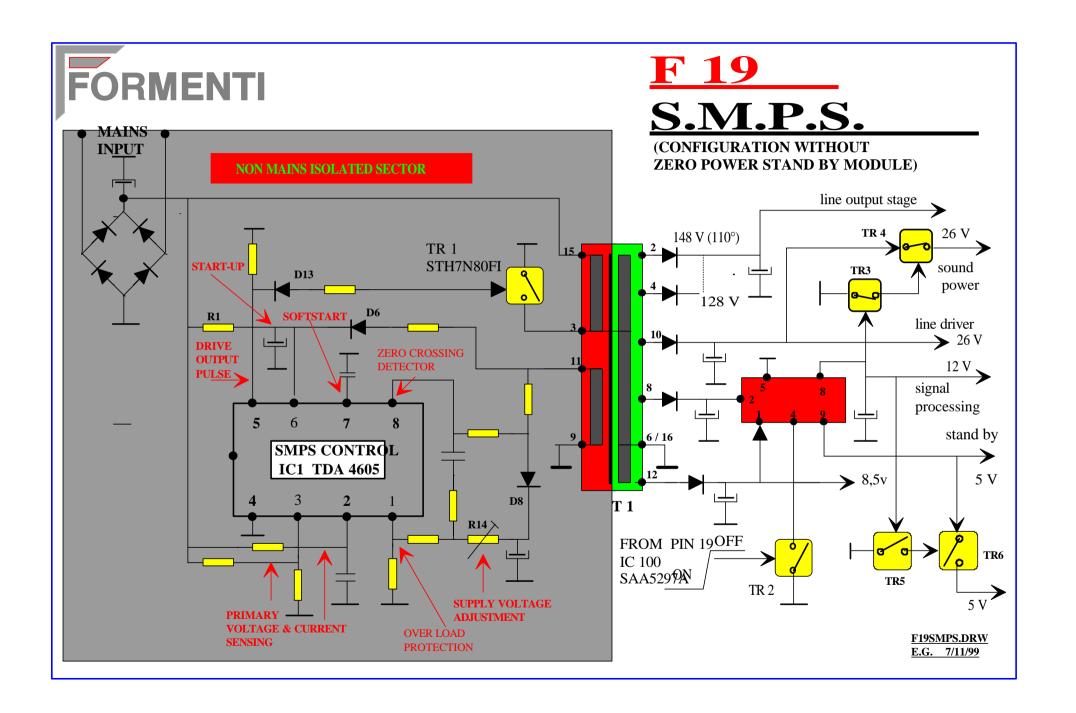

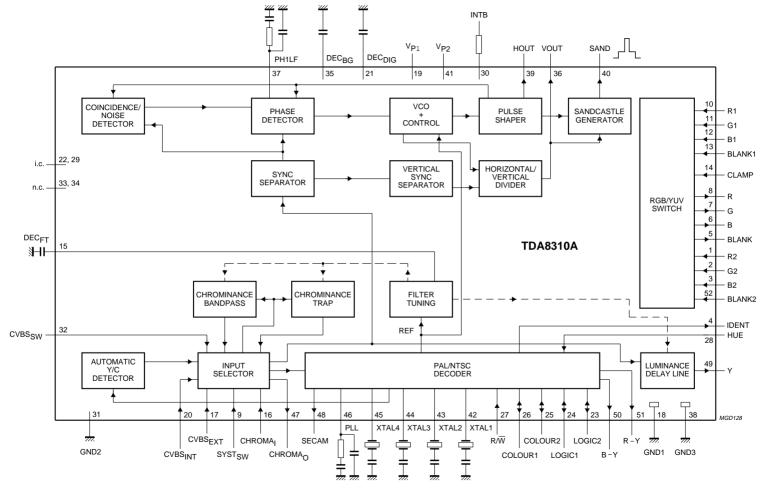

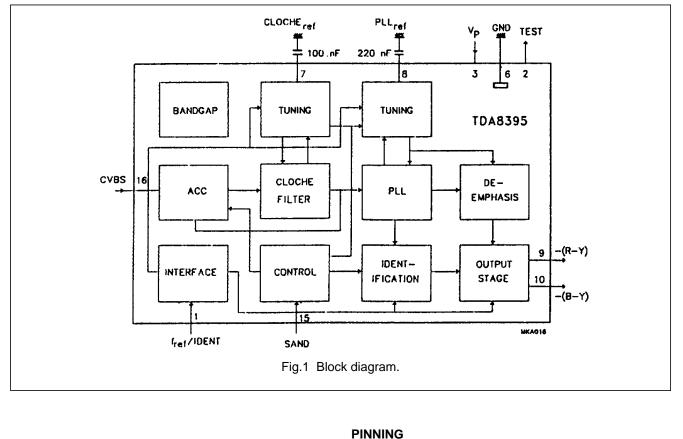

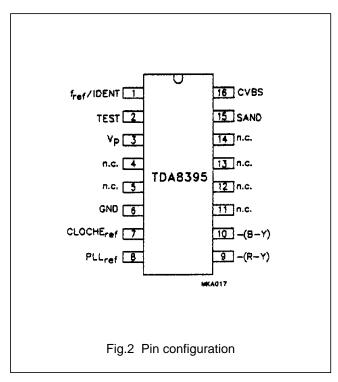

As we can see from the block diagram the chassis is equipped with the most recent Integrated Circuit like the one chip TV processor TDA884x that does include all the low level signal processing including Video, Audio, synchronisation process, and chroma decoder. (see more detail at the "TDA884x FAMILY SPECIFICATION" paragraph), and the Sound Processor TDA9875A that perform all sound function including digital decoding of NICAM signals. (see more detail at the "TDA9870A & tda9875A MAIN CHARACTERISTICS" paragraph).

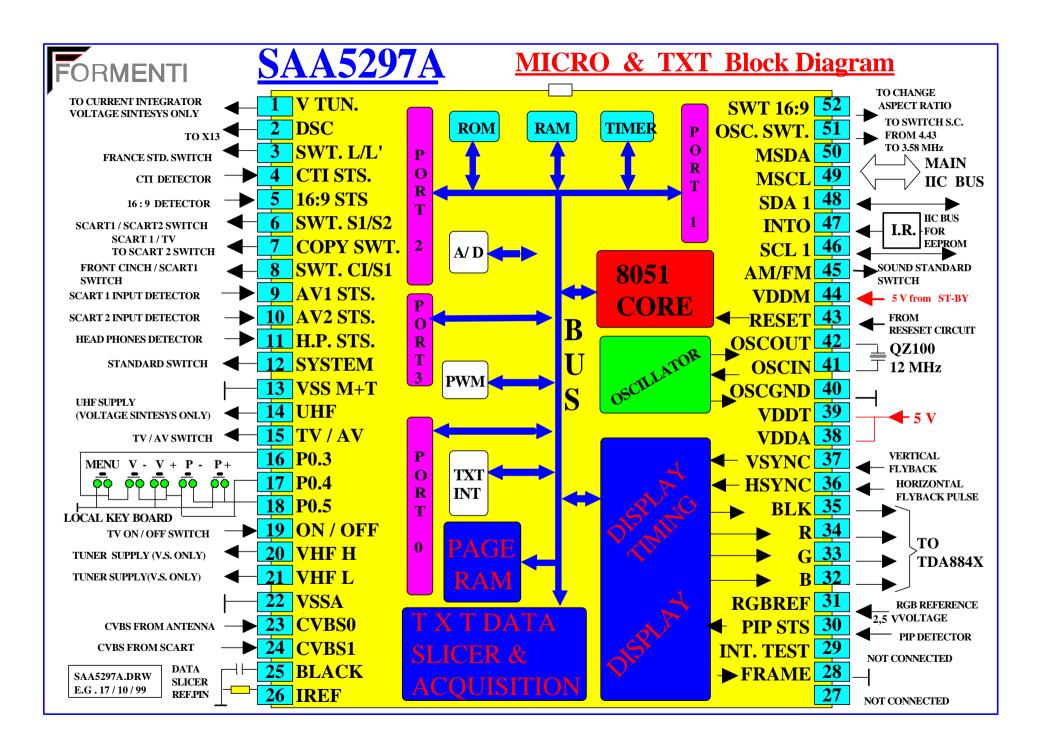

The above mentioned devices are driven by an Integrated Circuit that does include the microcontroller function with 64 K ROM and the TELETEXT acquisition and 8 pages RAM. (SAA5297A)

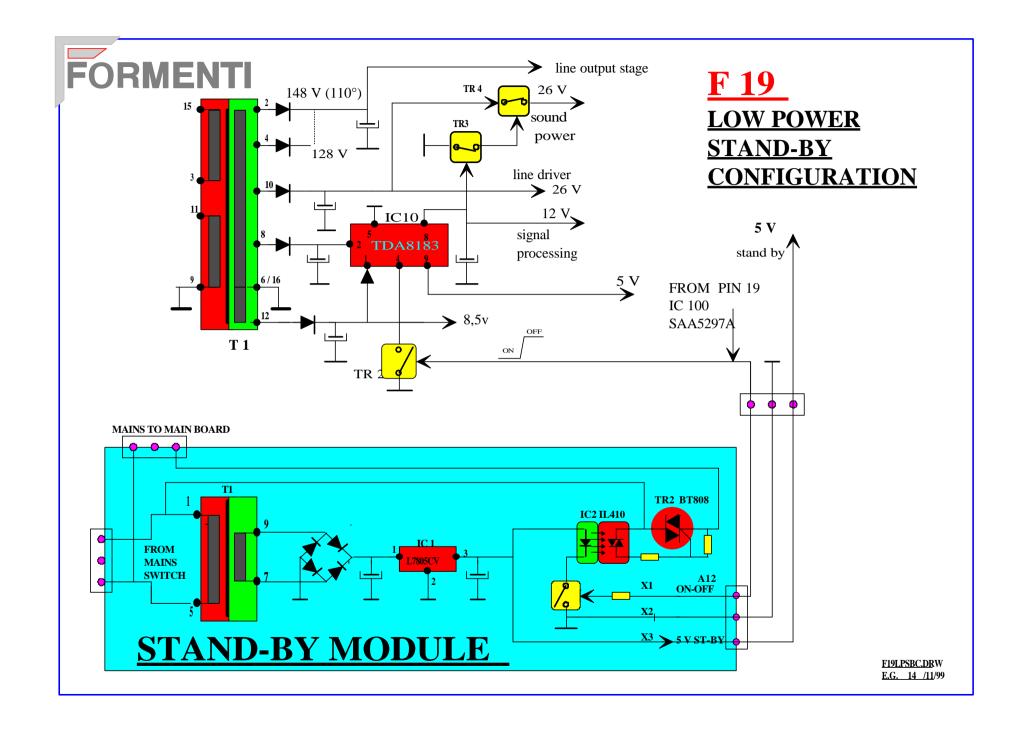

In the **F19** chassis there are, besides the stereo one, two possible module that are performing "FEATURES" like PIP (picture in picture) and / or CTI (colour transients improvement) and 4 by 3 to 16 by 9 signal processing. One further module is dedicated to the so called "Zero Power Stand By"

A 26 Key Remote Control is performing the full control for the end- used but can also be used in " SERVICE MODE" to control and adjust, without open the back cover of the TV set all the necessary functions.

With the 5 "LOCAL KEY BOARD" button all the end user function can also be performed

When the TV set is equipped with a PLL tuner the microcontroller recognise it and the tuning method became a frequency synthesis system if not it work as a voltage tuning system (provided all necessary components are mounted)

The TV make use of a multilevel MENU (activated both by the Remote Control and Local Keyboard) using five selectable languages (Italian, German, English, France, end Spanish) with which it is possible to control sequentially all video and sound value, to adjust several parameter like picture format, sound response, sleep timer etc., and to set others important parameter like standard, select country for automatic tuning and sort etc.

Here below a list of the characteristics of the TV se

## TV SET CHARACTERISTICS (MONO & STEREO)

|                                     | 1                           |

|-------------------------------------|-----------------------------|

| PICTURE TUBE SIZE:                  |                             |

| • 4:3 ASPECT RATIO                  | 21" / 25" / 28" / 29" / 34" |

| • 16:9 ASPECT RATIO                 | 28 " / 32"                  |

| • STANDARD                          |                             |

| • R.F. (ANTENNA) (FOR FREQ. SYNTH.) | CCIR (B/G/L/L'/D/K/I)       |

| VIDEO (SCART & CINCH)               | B/G/L/L'/D/K/I/M/N          |

| COLOUR (MAX. THREE STANDARDS)       | PAL / SECAM / NTSC          |

| SOUND STANDARD:                     | B/G/L/L'/D/K/I              |

| * MONO                              | AM & FM                     |

| * STEREO                            | A2 OR NICAM                 |

| TUNING SYSTEM SELECTABLE:           | FACTORY OPTION              |

| FREQUENCY SYTHETIZER                |                             |

| TOTAL AVAILABLE CHANNEL NUMBER      | 200                         |

| CHANNEL IN ONE RF STANDARD UP TO    | 100                         |

| NUMBER OF PROGRAM                   | 100                         |

| DIRECT PROGRAM & CHANNEL CALL WITH  | 1, OR 2 OR 3 DIGIT          |

| PROGRAM & CHANNEL STEP UP AND DOWN  | YES                         |

| VOLTAGE SYNTHESISER                 |                             |

| CABLE & HYPERBAND CHANNEL           | YES                         |

| SWITCHABLE AFC                      | YES                         |

| AUTOMATIC SEARCH TUNING             | YES                         |

| A S T WITH AUTO SORT                | YES                         |

| AUDIO SECTION                       |                             |

| POWER                               |                             |

| • MONO                              | 6 W RMS.                    |

| • STEREO                            | 2 x 6 W RMS.                |

| EXTERNAL CONNECTION                 |                             |

| HEADPHONE                           | STEREO SET ONLY             |

| • LOUDSPEAKERS                      | INTERNAL L.S. SWITCHED      |

| A / V INPUT / OUTPUT                |                             |

| FRONT PANEL CINCH                   | A / V INPUT                 |

| • I FULL SCART (CVBS, STEREO, RBA)  | MULTIMEDIA INPUT OUTPUT     |

| SCART (CVBS & STEREO IN / OUT)      | VCR, HI.FI, SATELLITE, ETC  |

| SCART A TO SCART B LOOP THROUGH     | FOR PROGRAMS DUBBING        |

| TXT                                 | PANEUROPEAN CHARACTER SET   |

| • LEVEL 1                           | 8 PAGES                     |

| • LEVEL 1,5 (FASTEXT)               | 7 PAGES                     |

| FEATURES                            |                             |

| CTI (COLOUR TRANSIENT IMPROVEMENT)  | OPTION                      |

| • 16:9 TO 4:3 VIDEO COMPRESSION     | ONLY FOR 16:9 TV SET        |

| VERTICAL ZOOM OUT                   | 3 LEVEL                     |

| MENU DRIVEN SYSTEM                  |                             |

| EASY TO USE REMOTE CONTROL          |                             |

| REMOTE CONTROL WITH "SERVICE" USE   | NOT ACCESSIBLE TO END USER  |

| • PIP                               | OPTION                      |

|                                     | •                           |

# FORMENTI

# F19 TUNING

## **SAA529XA FAMILY MAIN CHARACTERISTICS**

#### **FEATURES**

#### General

- · Single chip microcontroller with integrated teletext decoder

- Single +5 V power supply

- Single crystal oscillator for teletext decoder, display and microcontroller

- Teletext function can be powered-down independent of microcontroller function for reduced power consumption in standby

- Pin compatibility throughout family.

#### Microcontroller

- 80C51 microcontroller core

- 16/32/64 kbyte mask programmed ROM

- 256/768/1280 bytes of microcontroller RAM

- Eight 6-bit Pulse Width Modulator (PWM) outputs for control of TV analog signals

- One 14-bit PWM for Voltage Synthesis Tuner control

- Four 8-bit Analog-to-Digital converters

- 2 high current open-drain outputs for directly driving LEDs etc.

- I 2 C-bus interface

- External ROM and RAM capability on QFP80 package version.

#### **Teletext acquisition**

- 1 page and 10 page Teletext version

- Acquisition of 525-line and 625-line World System Teletext, with automatic selection

- Acquisition and decoding of VPS data (PDC system A)

- Page clearing in under 64 s (1 TV line)

- Separate storage of extension packets (SAA5296/7, SAA5296/7A and SAA5496/7)

- Inventory of transmitted Teletext pages stored in the Transmitted Page Table (TPT)

end Subtitle Page Table (SPT) (SAA5296/7, SAA5296/7A and SAA5496/7)

- Automatic detection of FASTEXT transmission

- Real-time packet 26 engine for processing accented (and other) characters

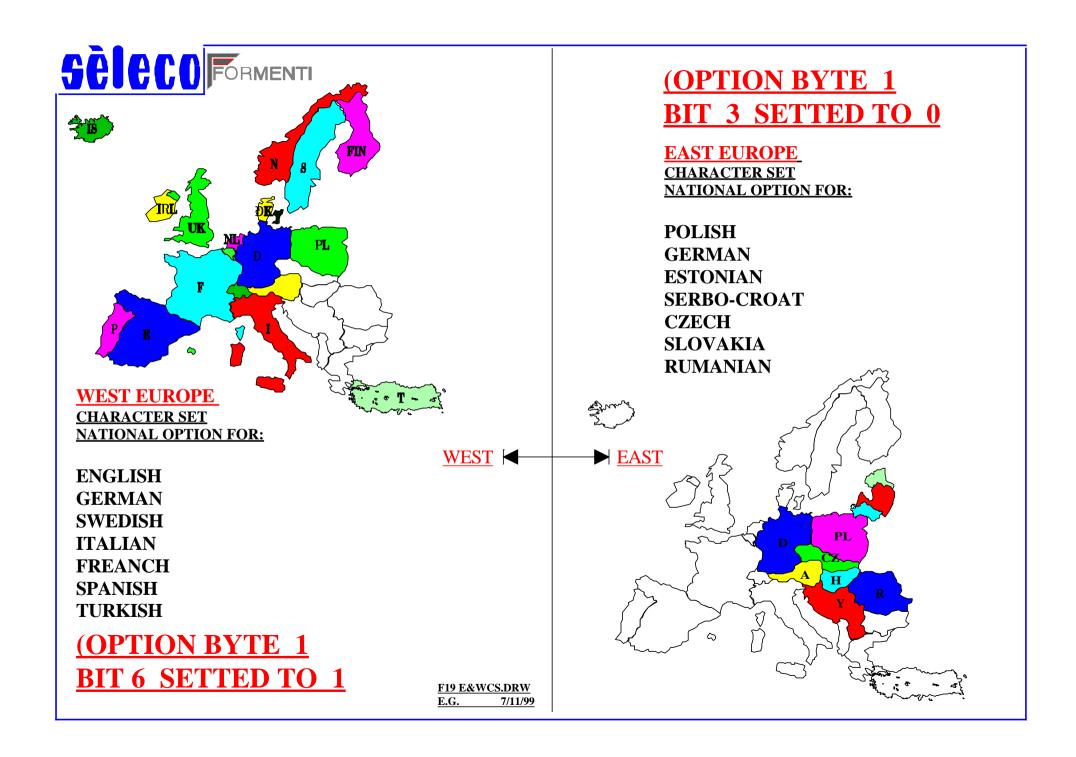

- Comprehensive Teletext language coverage

- Video signal quality detector.

#### **Teletext Display**

- 525-line and 625-line display

- 12 10 character matrix

- Double height, width and size On-Screen Display (OSD)

- Definable border colour

- Enhanced display features including meshing and shadowing

- 260 characters in mask programmed ROM

- Automatic FRAME output control with manual override

- RGB push-pull output to standard decoder ICs

- Stable display via slave synchronisation to horizontal sync and vertical sync.

#### Additional features of SAA529xA devices

Wide Screen Signalling (WSS) bit decoding (line 23).

#### **2 GENERAL DESCRIPTION**

The SAA529x, SAA529xA and SAA549x family of microcontrollers are a derivative of the Philips' industry-standard 80C51 microcontroller and are intended for use as the central control mechanism in a television receiver. They provide control functions for the television system and include an integrated teletext function.

The teletext hardware has the capability of decoding and displaying both 525-line and 625-line World System Teletext. The same display hardware is used both for Teletext and On-Screen Display, which means that the display features give greater flexibility to differentiate the TV set.

The family offers both 1 page and 10 page Teletext capability, in a range of ROM sizes. Increasing display capability is offered from the SAA5290 to the SAA5497.

#### **TELETEXT DECODER**

#### **Data slicer**

The data slicer extracts the digital teletext data from the incoming analog waveform. This is performed by sampling the CVBS waveform and processing the samples to extract the teletext data and clock.

#### **Acquisition timing**

The acquisition timing is generated from a logic level positive-going composite sync signal VCS. This signal is generated by a sync separator circuit which adaptively slices the sync pulses. The acquisition clocking and timing are locked to the VCS signal using a digital phase-locked-loop. The phase error in the acquisition phase-locked-loop is detected by a signal quality circuit which disables acquisition if poor signal quality is detected.

#### **Teletext acquisition**

This family is capable of acquiring 625-line and 525-line World System Teletext see "World System Teletext and Data Broadcasting System". Teletext pages are identified by seven numbers: magazine (page hundreds), page tens, page units, hours tens, hours units, minutes tens and minutes units. The last four digits, hours and minutes, are known as the subcode, and were originally intended to be time related, hence their names.

For the ten page device, each packet can only be written into one place in the teletext RAM so if a page matches more than one of the page requests the data is written into the area of memory corresponding to the lowest numbered matching page request.

At power-up each page request defaults to any page, hold on and error check Mode 0.

#### Rolling headers and time

When a new page has been requested it is conventional for the decoder to turn the header row of the display green and to display each page header as it arrives until the correct page has been found.

#### **Error checking**

Before teletext packets are written into the page memory they are error checked. The error checking carried out depends on the packet number, the byte number, the error check mode bits in the page request data and the TXT1.8 BIT bit. If an uncorrectable error occurs in one of the Hamming checked addressing and control bytes in the page header or in the Hamming checked bytes in packet 8/30, bit 4 of the byte written into the memory is set, to act as an error flag to the software. If uncorrectable errors are detected in any other Hamming checked data the byte is not written into the memory.

#### Packet 26 processing

One of the uses of packet 26 is to transmit characters which are not in the basic teletext character set. The family automatically decodes packet 26 data and, if a character corresponding to that being transmitted is available in the character set, automatically writes the appropriate character code into the correct location in the teletext memory. This is not a full implementation of the packet 26 specification allowed for in level 2 teletext, and so is often referred to as level 1.5.

By convention, the packets 26 for a page are transmitted before the normal packets. To prevent the default character data overwriting the packet 26 data the device incorporates a mechanism which prevents packet 26 data from being overwritten.

#### **Fastext detection**

When a packet 27, designation code 0 is detected, whether or not it is acquired, the TXT13.FASTEXT bit is set. If the device is receiving 525-line teletext, a packet X/0/27/0 is required to set the flag. The flag can be reset by writing a logic 0 into the SFR bit.

When a packet 8/30 is detected, or a packet 4/30 when the device is receiving a 525-line transmission, the TXT13.Pkt 8/30 is set. The flag can be reset by writing a logic 0 into the SFR bit.

#### THE DISPLAY

#### Introduction

The capabilities of the display are based on the requirements of level 1 teletext, with some enhancements for use with locally generated on screen displays. The display consists of 25 rows each of 40 characters, with the characters displayed being those from rows 0 to 24 of the basic page memory. If the TXT7.STATUS ROW TOP bit is set row 24 is displayed at the top of the screen, followed by row 0, but normally memory rows are displayed in numerical order. The teletext memory stores 8 bit character codes which correspond to a number of displayable characters and control characters, which are normally displayed as spaces. The character set of the device is described in more detail below.

#### **Character matrix**

Each character is defined by a matrix 12 pixels wide and 10 pixels high. When displayed, each pixel is 1 12 s wide and 1 TV line, in each field, high.

#### **East/West selection**

In common with their predecessors, these devices store teletext pages as a series of 8 bit character codes which are interpreted as either control codes (to change colour, invoke flashing etc.) or displayable characters. When the control characters are excluded, this gives an addressable set of 212 characters at any given time.

#### **National option characters**

The meanings of some character codes between 20H and 7FH depend on the C12 to C14 language control bits from the teletext page header.

The interpretation of the C12 to C14 language control bits is dependent on the East/West bit.

#### **On-Screen Display characters**

Character codes 80H to 9FH are not addressed by the teletext decoding hardware. An editor is available to allow these characters to be redefined by the customer. The alternative character shapes in columns 8a and 9a (SAA549x only) can be displayed when the 'graphics' serial attribute is set. This increases the number of customer definable characters to 64.

#### **Clock generator**

The oscillator circuit is a single-stage inverting amplifier in a Pierce oscillator configuration. The circuitry between XTALIN and XTALOUT is basically an inverter biased to the transfer point. A crystal must be used as the feedback element to complete the oscillator circuitry. It is operated in parallel resonance. XTALIN is the high gain amplifier input and XTALOUT is the output. To drive the device externally XTALIN is driven from an external source and XTALOUT is left open-circuit.

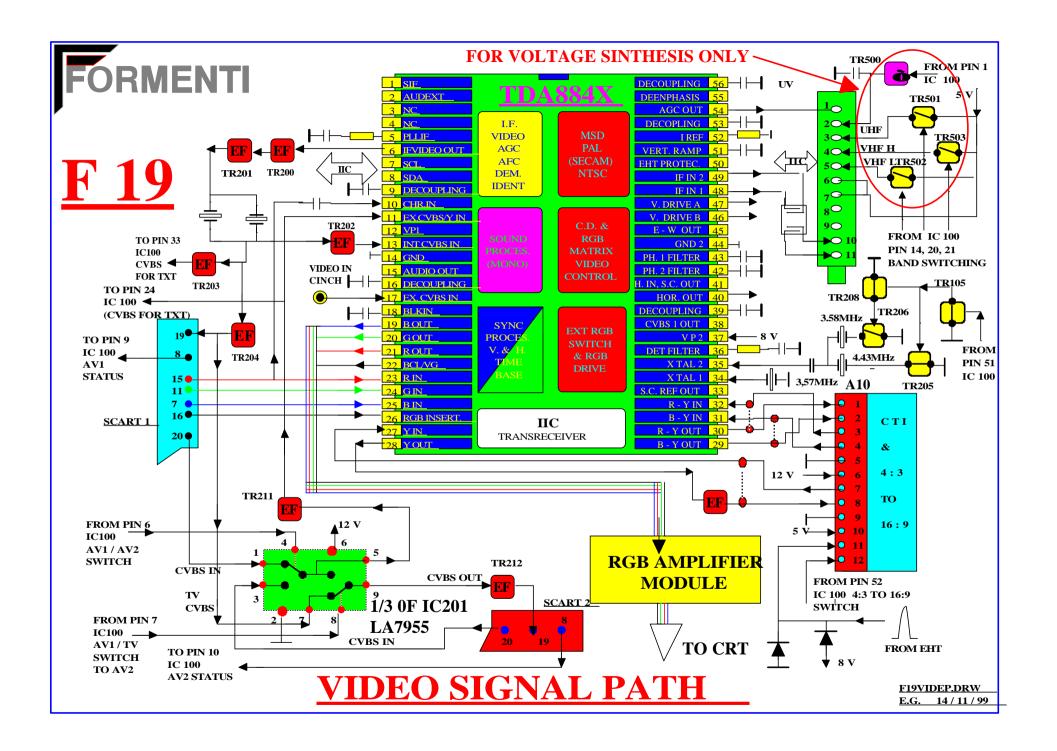

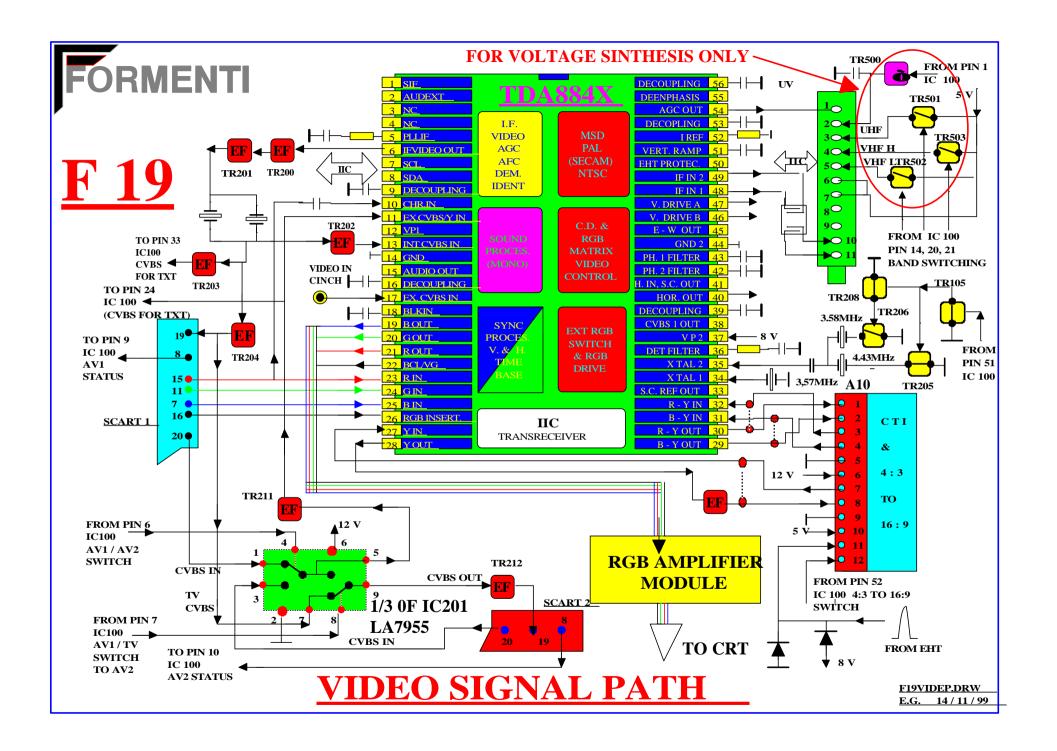

# **VIDEO**

**SIGNAL**

**PROCESSING**

#### Reset signal

The externally applied RESET signal (active HIGH) is used to initialize the microcontroller core, in addition to the teletext decoder. However, the teletext decoder incorporates a separate internal reset function which is activated on the rising edge of the analog supply pin, V<sub>DDA</sub>. The purpose of this internal reset circuit is to initialize the teletext decoder when returning from the "text standby mode".

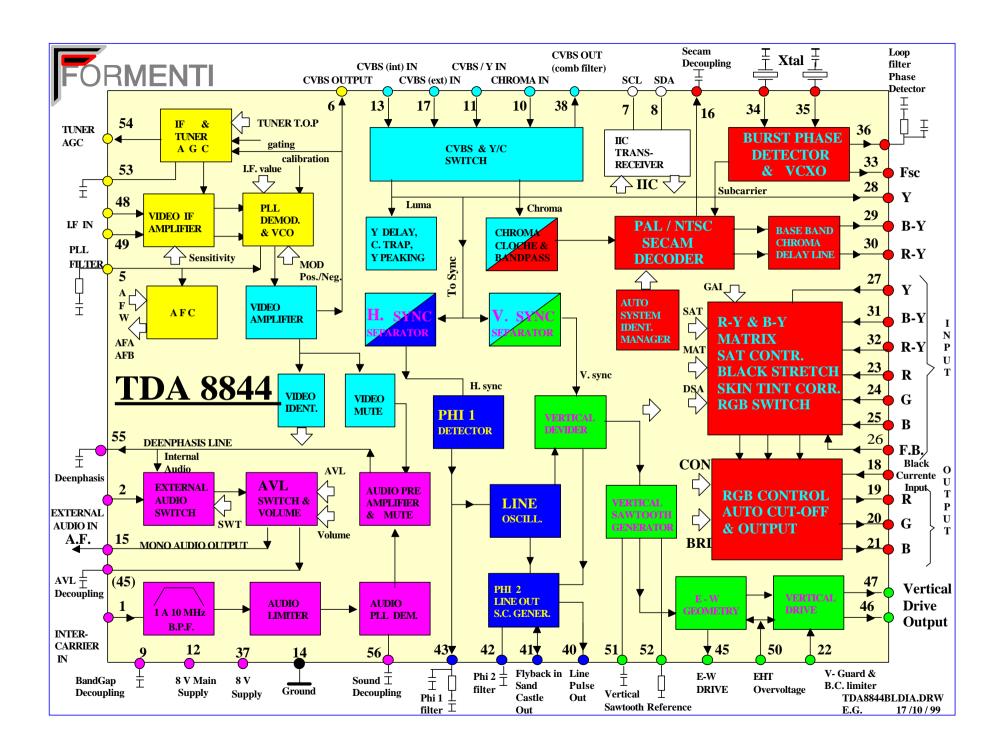

## **TDA884X FAMILY SPECIFICATION**

#### **FEATURES**

The following features are available in all IC's:

- Multi-standard vision IF circuit with an alignment-freePLL demodulator without external components

- Alignment-free multi-standard FM sound demodulator(4.5 MHz to 6.5 MHz)

- Audio switch

- Flexible source selection with CVBS switch andY(CVBS)/C input so that a comb filter can be applied

- Integrated chrominance trap circuit

- Integrated luminance delay line

- Asymmetrical peaking in the luminance channel with a(defeatable) noise coring function

- Black stretching of non-standard CVBS or luminancesignals

- Integrated chroma band-pass filter with switchablecentre frequency

- Dynamic skin tone control circuit

- Blue stretch circuit which offsets colours near whitetowards blue

- RGB control circuit with "Continuous CathodeCalibration" and white point adjustment

- Possibility to insert a "blue back" option when no videosignal is available

- Horizontal synchronization with two control loops and alignment-free horizontal oscillatoroptimised N2 application. Functionally the IC series is split up is 3 categories, viz:

- Versions intended to be used in economy TV receiverswith all basic functions (envelope:

S-DIP 56 and QFP 64)

- Versions with additional features like E-W geometrycontrol, H-V zoom function and YUV interface which are intended for TV receivers with 110° picture tubes(envelope: S-DIP 56)

- Versions which have in addition a second RGB inputwith saturation control and a second

CVBS output (envelope: QFP 64)

- Vertical count-down circuit

- Vertical driver optimised for DC-coupled vertical outputstages

#### **GENERAL DESCRIPTION**

The various versions of the TDA 884X/5X series arel 2 C-bus controlled single chip TV processors which are

intended to be applied in PAL, NTSC, PAL/NTSC and multi-standard television receivers. The N2 version is pin and application compatible with the N1 version, however,a new feature has been added which makes the N2 more attractive. The IF PLL demodulator has been replaced by an alignment-free IF PLL demodulator with internal VCO (no tuned circuit required). The setting of the various frequencies (33.4, 33.9, 38.9, 45.75 and 58.75 MHz) can be made via the I 2 C-bus.

Because of this difference the N2 version is compatible with the N1, however, N1 devices cannot be used in an optimized N2 application

Functionally the IC series is split up is 3 categories, viz:

- Versions intended to be used in economy TV receivers with all basic functions (envelope: S-DIP 56 and QFP 64)

- Versions with additional features like E-W geometry control, H-V zoom function and YUV interface which are intended for TV receivers with 110° picture tubes (envelope: S-DIP 56)

- Versions which have in addition a second RGB input with saturation control and a second CVBS output (envelope: QFP 64)

#### **FUNCTIONAL DESCRIPTION**

#### **Vision IF amplifier**

The IF-amplifier contains 3 ac-coupled control stages with a total gain control range which is higher then 66 dB. The sensitivity of the circuit is comparable with that of modern

#### IF-IC's.

The video signal is demodulated by means of an alignment-free PLL carrier regenerator with an internal VCO. This VCO is calibrated by means of a digital control circuit which uses the X-tal frequency of the colour decoder as a reference. The frequency setting for the various standards (33.4, 33.9, 38, 38.9, 45.75 and 58.75 MHz) is realised via the I 2 C-bus. To get a good performance for phase modulated carrier signals the control speed of the PLL can be increased by means of the FFI bit.

The AFC output is generated by the digital control circuit of the IF-PLL demodulator and can be read via the I 2 C-bus.

For fast search tuning systems the window of the AFC can be increased with a factor 3. The setting is realised with the AFW bit. The AFC data is valid only when the horizontal PLL is in lock (SL = 1)

Depending on the type the AGC-detector operates on top-sync level (single standard versions) or on top sync and top white- level (multi standard versions). The demodulation polarity is switched via the I 2 C-bus. The AGC detector time-constant capacitor is connected externally. This mainly because of the flexibility of the application. The time-constant of the AGC system during positive modulation is rather long to avoid visible variations of the signal amplitude. To improve the speed of the AGC system a circuit has been included which detects whether the AGC detector is activated every frame period. When during 3 field periods no action detected the speed of the system is increased. For signals without peak white information the system switches automatically to a gated black level AGC. Because a black level clamp pulse is required for this way of operation the circuit will only switch to black level AGC in the internal mode.

The circuits contain a video identification circuit which is independent of the synchronisation circuit. Therefore search tuning is possible when the display section of the receiver is used as a monitor. However, this ident circuit cannot be made as sensitive as the slower sync ident circuit (SL) and we recommend to use both ident outputs to obtain a reliable search system. The ident output is supplied to the tuning system via the I 2 C-bus. The input of the identification circuit is connected to pin 13 (S-DIP 56 devices), the "internal" CVBS input (see Fig.6).

This has the advantage that the ident circuit can also be made operative when a scrambled signal is received (descrambler connected between pin 6 (IF video output) and pin 13). A second advantage is that the ident circuit can be used when the IF amplifier is not used (e.g. with built-in satellite tuners).

The video ident circuit can also be used to identify the selected CBVS or Y/C signal. The switching between the 2 modes can be realised with the VIM bit.

#### Video switches

The circuits have two CVBS inputs (internal and external CVBS) and a Y/C input. When the Y/C input is not required the Y input can be used as third CVBS input. The switch configuration is given in Fig.6. The selection of the various sources is made via the I 2 C-bus.

For the TDA 884X devices the video switch configuration is identical to the switch of the TDA 8374/75 series. So the circuit has one CVBS output (amplitude of 2 VP-P for the TDA884X series) and the I 2 C-bus control is similar to that of the TDA 8374/75. For the TDA 885X IC's the video switch circuit has a second output (amplitude of 1 VP-P) which can be set independently of the position of the first output. The input signal for the decoder is also available on the CVBS1-output.

Therefore this signal can be used to drive the Teletext decoder. If S-VHS is selected for one of the outputs the luminance and chrominance signals are added so that a CVBS signal is obtained again.

#### **Sound circuit**

The sound bandpass and trap filters have to be connected externally. The filtered intercarrier signal is fed to a limiter circuit and is demodulated by means of a PLL demodulator. This PLL circuit tunes itself automatically to the incoming carrier signal so that no adjustment is required.

The volume is controlled via the I 2 C-bus. The deemphasis capacitor has to be connected externally. The non-controlled audio signal can be obtained from this pin (via a buffer stage).

The FM demodulator can be muted via the I 2 C-bus. This function can be used to switch-off the sound during a channel change so that high output peaks are prevented.

The TDA 8840/41/42/46 contain an Automatic Volume Levelling (AVL) circuit which automatically stabilises the audio output signal to a certain level which can be set by the viewer by means of the volume control. This function prevents big audio output fluctuations due to variations of the modulation depth of the transmitter. The AVL function can be activated via the I 2 C-bus.

#### Synchronisation circuit

The sync separator is preceded by a controlled amplifier which adjusts the sync pulse amplitude to a fixed level. These pulses are fed to the slicing stage which is operating at 50% of the amplitude. The separated sync pulses are fed to the first phase detector and to the coincidence detector. This coincidence detector is used to detect whether the line oscillator is synchronised and can also be used for transmitter identification. This circuit can be made less sensitive by means of the STM bit. This mode can be used during search tuning to avoid that the tuning system will stop at very weak input signals. The first PLL has a very high statical steepness so that the phase of the picture is independent of the line frequency.

The horizontal output signal is generated by means of an oscillator which is running at twice the line frequency. Its frequency is divided by 2 to lock the first control loop to the incoming signal. The time-constant of the loop can be forced by the I 2 C-bus (fast or slow). If required the IC can select the time-constant depending on the noise content of the incoming video signal.

The free-running frequency of the oscillator is determined by a digital control circuit which is locked to the reference signal of the colour decoder. When the IC is switched-on the horizontal output signal is suppressed and the oscillator is calibrated as soon as all sub-address bytes have been sent. When the frequency of the oscillator is correct the horizontal drive signal is switched-on. To obtain a smooth switching-on and switching-off behaviour of the horizontal output stage the horizontal output frequency is doubled during switch-on and switch-off (slow start/stop). During that time the duty cycle of the output pulse has such a value that maximum safety is obtained for the output stage.

To protect the horizontal output transistor the horizontal drive is immediately switched off when a power-on-reset is detected. The drive signal is switched-on again when the normal switch-on procedure is followed, i.e. all sub-address bytes must be sent and after calibration the horizontal drive signal will be released again via the slow start procedure. When the coincidence detector indicates an out-of-lock situation the calibration procedure is repeated.

The circuit has a second control loop to generate the drive pulses for the horizontal driver stage. The horizontal output is gated with the flyback pulse so that the horizontal output transistor cannot be switched-on during the flyback time.

Via the I 2 C-bus adjustments can be made of the horizontal and vertical geometry. The vertical sawtooth generator drives the vertical output drive circuit which has a differential output current. For the E-W drive a single ended current output is available. A special

feature is the zoom function for both the horizontal and vertical deflection and the vertical scroll function which are available in some versions. When the horizontal scan is reduced to display 4:3 pictures on a 16:9 picture tube an accurate video blanking can be switched on to obtain well defined edges on the screen.

Overvoltage conditions (X-ray protection) can be detected via the EHT tracking pin. When an overvoltage condition is detected the horizontal output drive signal will be switched-off via the slow stop procedure but it is also possible that the drive is not switched-off and that just a protection indication is given in the I 2 C-bus output byte.

The choice is made via the input bit PRD. The IC's have a second protection input on the  $\phi 2$  filter capacitor pin. When this input is activated the drive signal is switched-off immediately and switched-on again via the slow start procedure. For this reason this protection input can be used as "flash protection".

The drive pulses for the vertical sawtooth generator are obtained from a vertical countdown circuit. This countdown circuit has various windows depending on the incoming signal (50 Hz or 60 Hz and standard or non standard). The countdown circuit can be forced in various modes by means of the I 2 C-bus. During the insertion of RGB signals the maximum vertical frequency is increased to 72 Hz so that the circuit can also synchronise on signals with a higher vertical frequency like VGA. To obtain short switching times of the countdown circuit during a channel change the divider can be forced in the search window by means of the NCIN bit. The vertical deflection can be set in the deinterlace mode via the I 2 C bus. To avoid damage of the picture tube when the vertical deflection fails the guard output current of the TDA 8350/51 can be supplied to the beam current limiting input. When a failure is detected the RGB-outputs are blanked and a bit is set (NDF) in the status byte of the I 2 C-bus. When no vertical deflection output stage is connected thisguard circuit will also blank the output signals. This can be overruled by means of the EVG bit.

#### **Chroma and luminance processing**

The circuits contain a chroma bandpass and trap circuit. The filters are realised by means of gyrator circuits and

they are automatically calibrated by comparing the tuning frequency with the X-tal frequency of the decoder. The luminance delay line and the delay for the peaking circuit are also realised by means of gyrator circuits. The centre frequency of the chroma bandpass filter is switchable via the I 2 C-bus so that the performance can be optimised for

"front-end" signals and external CVBS signals. During SECAM reception the centre frequency of the chroma trap is reduced to get a better suppression of the SECAM carrier frequencies. All IC's have a black stretcher circuit which corrects the black level for incoming video signals which have a deviation between the black level and the blanking level (back porch). The timeconstant for the black stretcher is realised internally.

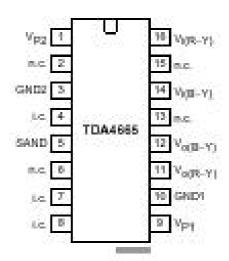

The resolution of the peaking control DAC has been increased to 6 bits. All IC's have a defeatable coringfunction in the peaking circuit. Some of these IC's have a YUV interface (see table on page 2) so that picture improvement IC's like the TDA 9170 (Contrast improvement), TDA 9177 (Sharpness improvement) and TDA 4556/66 (CTI) can be applied. When the CTI IC's are applied it is possible to increase the gain of the luminance channel by means of the GAI bit in subaddress 03 so that the resulting RGB output signals are not affected.

#### Colour decoder

Depending on the IC type the colour decoder can decode PAL, PAL/NTSC or PAL/NTSC/SECAM signals. The PAL/NTSC decoder contains an alignment-free X-tal oscillator, a killer circuit and two colour difference demodulators. The 90° phase shift for the reference signal is made internally.

The IC's contain an Automatic Colour Limiting (ACL) circuit which is switchable via the I 2 C-bus and which prevents that oversaturation occurs when signals with a high chroma-to-burst ratio are received. The ACL circuit is designed such that it only reduces the chroma signal and not the burst signal. This has the advantage that the colour sensitivity is not affected by this function. The SECAM decoder contains an auto-calibrating PLL demodulator which has two references, viz: the 4.4 MHz sub-carrier frequency which is obtained from the X-tal oscillator which is used to tune the PLL to the desired free-running frequency and the bandgap reference to obtain the correct absolute value of the output signal. The VCO of the PLL is calibrated during each vertical blanking period, when the IC is in search or SECAM mode.

The frequency of the active X-tal is fed to the Fsc output (pin 33) and can be used to tune an external comb filter (e.g. the SAA 4961).

The base-band delay line (TDA 4665 function) is integrated in the PAL/SECAM IC's and in the NTSC IC TDA 8846A. In the latter IC it improves the cross colour performance (chroma comb filter). The demodulated colour difference signals are internally supplied to the delay line. The colour difference matrix switches automatically between PAL/SECAM and NTSC, however, it is also possible to fix the matrix in the PAL standard.

The "blue stretch" circuit is intended to shift colour near "white" with sufficient contrast values towards more blue to obtain a brighter impression of the picture.

Which colour standard the IC's can decode depends on the external X-tals. The X-tal to be connected to pin 34 must have a frequency of 3.5 MHz (NTSC-M, PAL-M or PAL-N) and pin 35 can handle X-tals with a frequency of 4.4 and 3.5 MHz. Because the X-tal frequency is used to tune the line oscillator the value of the X-tal frequency must be given to the IC via the I 2 C-bus. It is also possible to use the IC in the so called "Tri-norma" mode for South America. In that case one X-tal must be connected to pin 34 and the other 2 to pin 35. The switching between the 2 latter X-tals must be done externally. This has the consequence that the search loop of the decoder must be controlled by the  $\mu$ -computer. To prevent calibration problems of the horizontal oscillator the external switching between the 2 X-tals should be carried out when the oscillator is forced to pin 34. For a reliable calibration of the horizontal oscillator it is very important that the X-tal indication bits (XA and XB) are not corrupted. For this reason the X-tal bits can be read in the output bytes so that the software can check the I 2 C-bus transmission.

Under bad-signal conditions (e.g. VCR-playback in feature mode), it may occur that the colour killer is activated although the colour PLL is still in lock. When this killing action is not wanted it is possible to overrule the colour killer by forcing the colour decoder to the required standard and to activate the FCO-bit (Forced Colour On) in the control-5 subaddress.

The IC's contain a so-called "Dynamic skin tone (flesh) control" feature. This function is realised in the YUV domain by detecting the colours near to the skin tone. The correction angle can be controlled via the I 2 C-bus.

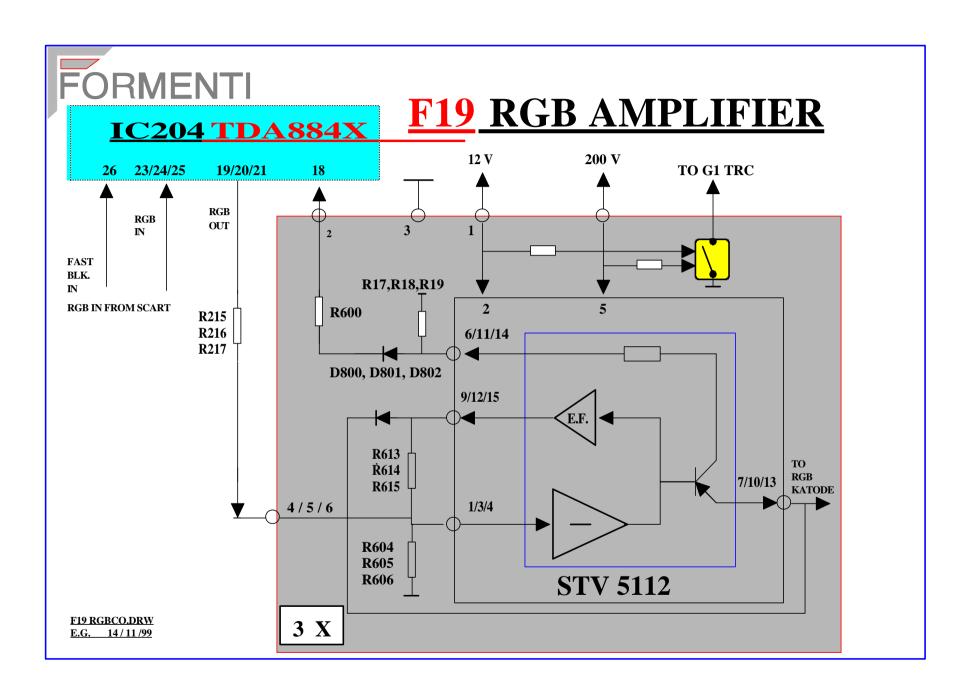

#### RGB output circuit and black-current stabilisation

The colour-difference signals are matrixed with the luminance signal to obtain the RGB-signals. The TDA 884X devices have one (linear) RGB input. This RGB signal can be controlled on contrast and brightness (like TDA 8374/75). By means of the IE1 bit the insertion blanking can be switched on or off. Via the IN1 bit it can be read whether the insertion pin has a high level or not.

The TDA 885X IC's have an additional RGB input. This RGB signal can be controlled on contrast, saturation and brightness. The insertion blanking of this input can be switched-off by means of the IE2 bit. Via the IN2 bit it can be read whether the insertion pin has a high level or not.

The output signal has an amplitude of about 2 volts black-to-white at nominal input signals and nominal settings of the controls. To increase the flexibility of the IC it is possible to insert OSD and/or teletext signals directly at the RGB outputs. This insertion mode is controlled via the insertion input (pin 26 in the S-DIP 56- and pin 38 in the QFP-64 envelope). This blanking action at the RGB outputs has some delay which must be compensated externally.

To obtain an accurate biasing of the picture tube a "Continuous Cathode Calibration" circuit has been developed. This function is realised by means of a 2-point black level stabilisation circuit. By inserting 2 test levels for each gun and comparing the resulting cathode currents with 2 different reference currents the influence of the picture tube parameters like the spread in cut-off voltage can be eliminated.

This 2-point stabilisation is based on the principle that the ratio between the cathode currents is coupled to the ratio between the drive voltages according to:

$$[I_{ki}/I_{k2}] = [V_{dr1}/V_{dr2}]$$

The feedback loop makes the ratio between the cathode currents lk1 and lk2 equal to the ratio between the reference currents (which are internally fixed) by changing the (black) level and the amplitude of the RGB output signals via 2 converging loops. The system operates in such a way that the black level of the drive signal is controlled to the cut-off point of the gun so that a very good grey scale tracking is obtained. The accuracy of the adjustment of the black level is just dependent on the ratio of internal currents and these can be made very accurately in integrated circuits. An additional advantage of the 2-point measurement is that the control system makes the absolute value of lk1 and lk2 identical to the internal reference currents. Because this adjustment is obtained by means of an adaption of the gain of the RGB control stage this control stabilises the gain of the complete channel (RGB output stage and cathode characteristic).

As a result variations in the gain figures during life will be compensated by this 2-point loop.

An important property of the 2-point stabilisation is that the off-set as well as the gain of the RGB path is adjusted by the feedback loop. Hence the maximum drive voltage for the cathode is fixed by the relation between the test pulses, the reference current and the relative gain setting of the 3 channels. This has the consequence that the drive level of the CRT cannot be adjusted by adapting the gain of the RGB output stage. Because different picture tubes may require different drive levels the typical "cathode drive level" amplitude can be adjusted by means of an I 2 C-bus setting. Dependent on the chosen cathode drive

level the typical gain of the RGB output stages can be fixed taking into account the drive capability of the RGB outputs (pins 19 to 21). More details about the design will be given in the application report.

The measurement of the "high" and the "low" current of the 2- point stabilisation circuit is carried out in 2 consecutive fields. The leakage current is measured in each field. The maximum allowable leakage current is 100  $\mu$ A When the TV receiver is switched-on the RGB output signals are blanked and the black current loop will try to set the right picture tube bias levels. Via the AST bit a choice can be made between automatic start-up or a start-up via the  $\mu$ -processor. In the automatic mode the RGB drive signals are switched-on as soon as the black current loop

has been stabilised. In the other mode the BCF bit is set to 0 when the loop is stabilised. The RGB drive can than be switched-on by setting the AST bit to 0. In the latter mod some delay can be introduced between the setting of the BCF bit and the switching of the AST bit so that switch-on effects can be suppressed. It is also possible to start-up the devices with a fixed internal delay (as with the TDA 837X and the TDA884X/5X N1). This mode is activated with the BCO bit.

The vertical blanking is adapted to the incoming CVBS signal (50 Hz or 60 Hz). When the flyback time of the vertical output stage is longer than the 60 Hz blanking time the blanking can be increased to the same value as that of the 50 Hz blanking. This can be set by means of the LBM bit.

For an easy (manual) adjustment of the Vg2 control voltage the VSD bit is available. When this bit is activated the black current loop is switched-off, a fixed black level is inserted at the RGB outputs and the vertical scan is switched-off so that a horizontal line is displayed on the screen. This line can be used as indicator for the Vg2 adjustment. Because of the different requirements for the optimum cut-off voltage of the picture tube the RGB output level is adjustable when the VSD bit is activated. The control range is  $2.5 \pm 0.7 \, \text{V}$  and can be controlled via the brightness control DAC. It is possible to insert a so called "blue back" back-ground level when no video is available. This feature can be activated via the BB bit in the control2 subaddress.

# F 19 FEATURE MODULE

**Colour Transient Improvment**

4:3 to 16:9 Signal Processing

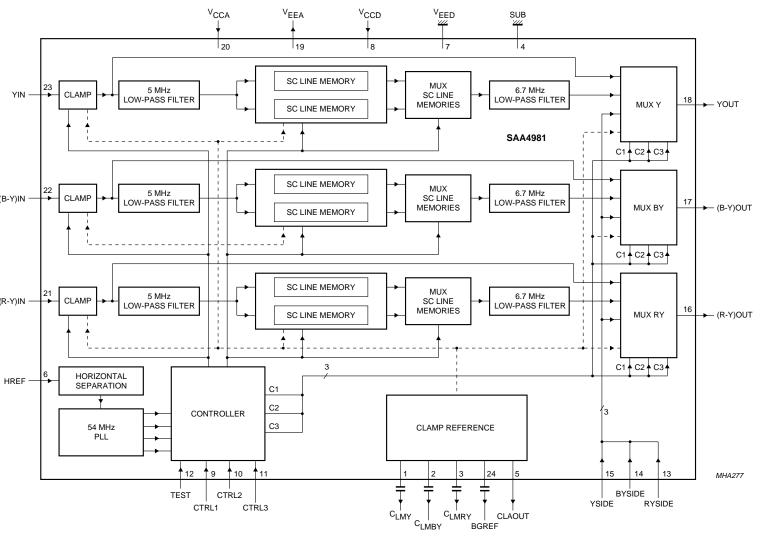

## **SAA4981**

## Monolithic integrated 16:9 **Compressor**

#### **FEATURES**

- Fixed horizontal compression by a factor of 4 ¤3 for most video standards

- Three fixed screen positions (left, centre and right)

- 5 MHz bandwidth

- Bypass function

- Inputs for luminance and chrominance of side panels

- Standard video inputs and outputs (Y, (B-Y) and (P-Y))

- Horizontal and vertical sync signals are not processed

- Pre filters and post filters on chip.

#### **GENERAL DESCRIPTION**

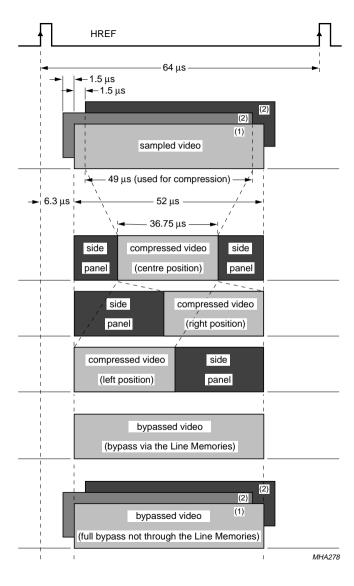

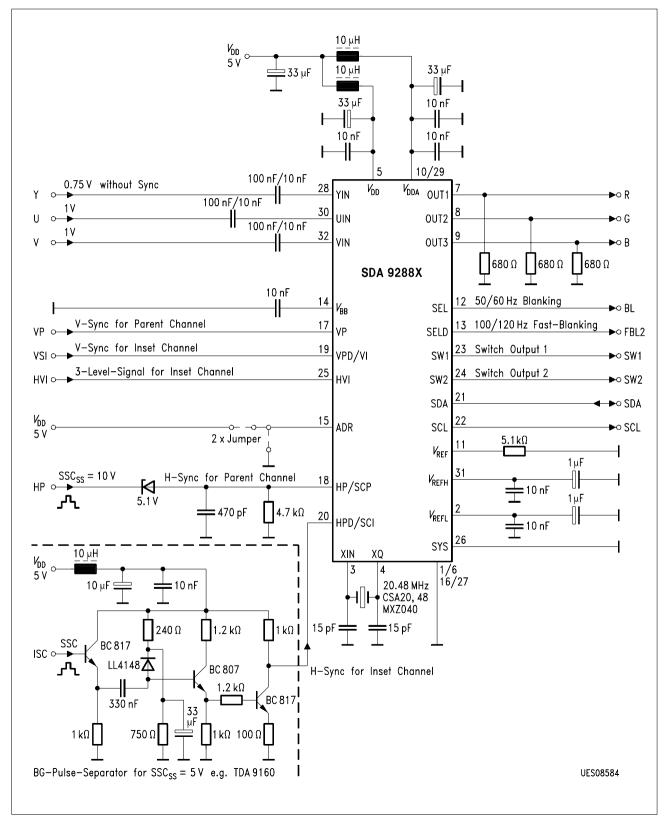

The integrated 16: 9 compressor is an IC which compresses the active part of a video line by a factor of 4 x3 from, for example, 52 ms to 39ms. This is necessary to display 4:3 video software on a 16:9 tube in the correctproportion. The capacitively coupled video inputs are Y, (B-Y) and (P-Y).

The synchronisation input HREF is a line frequencyreference signal. The bandwidth of the IC is up to 5 MHz and the signal delay is realized with SC Line Memories (Switched Capacitors Line Memories). The output of the 16:9 compressor also has the format Y, (B Y) and (P-Y) and provides the following two possibilities:

- 1. Bypass function (the input signal is not compressed)

- 2. Compressed video by a factor of 4 x3 with three different fixed screen positions (left, centre and right). The luminance and chrominance of the side panels are determined by the external signals YSIDE, BYSIDE and RYSIDE.

The horizontal compression is a time discrete and amplitude continuous signal processing. This provides pre and post filters which are realized on-chip.

#### **FUNCTIONAL DESCRIPTION**

#### Applicable video standards

The integrated 16: 9 compressor can be used for the following video standards; B, C, D, G, H, I, K, K1, L, M and N. standards D, I, K, K1 and L will show a reducedvideo bandwidth above 5 MHz.

#### Clamping circuit

The clamping circuits clamp the video input signals Y, (B-Y) and (P-Y) to the DC level of the clamp reference signal fed from the clamp reference circuit. This is necessary to ensure that the input signals are in the correct input voltage range for the 5 MHz low-pass filters and the SC line memories.

#### Internal pre filters

Before the signals are sampled in the time discrete and amplitude continuous area, low-pass filtering is necessary to avoid any aliasing. Even if the inputs have already been low-pass filtered further filtering is advantageous for the electromagnetic compatibility (EMC). The same transfer function is used for all three low-pass filters because of the same bandwidth for the luminance and chrominance signals (up to 5 MHz)

#### **SC** line memories

After the low-pass filters the input signals are fed to the SC line memories. The signals are sampled at a clock frequency of 13.5 MHz. One video line later the signals are read with a clock frequency of 18 MHz in the compression mode. The result of the different clock frequencies is a horizontal compression by a factor of 4  $\pm$ 3. The clocks and the horizontal starting pulses for the SC line memories are fed from the controller.

Two line memories are required for each signal path because in the compression mode, in one video line the signals are sampled to the SC line memories with 13.5 MHz and one video line later the signals are read with 18 MHz. In the bypass mode, via the SC line memories, in one video line the signals are sampled with 13.5 MHz and one video line later the signals are read with 13.5 MHz.

The SC line memories are suitable for signals with a bandwidth up to 5 MHz. With a multiplexer (MUX) behind the SC line memories, the sampled video signal is connected to the internal post filters.

Output multiplexer MUX Y, MUX (B-Y) and MUX (P-Y)

The output multiplexers are controlled via C1 and C2 fed from the controller. The multiplexers are used to connect one of the four input signals to the output and, also, enable fast switching.

The input signals of the multiplexers for one component

- The output signal of the post filter

- The uncompressed signal after the input clamping

- The clamping reference signal

- The signal for the side panel determined by YSIDE, BYSIDE and RYSIDE.

#### The horizontal separation circuit

The 54 MHz horizontal PLL is locked to the positive edge of the digital HREF signal, which is generated in the positive edge of the burst key of a sandcastle signal.

#### 54 MHz horizontal PLL

The 13.5 MHz clock frequency for the sampling clock and the 18 MHz clock frequency for the reading clock are generated in the 54 MHz horizontal PLL. The 13.5 MHzclock and the 18 MHz clock are line locked.

#### Clamp reference

Reference voltages are generated In the clamp reference block. These DC signals are used in the clamping circuits as input signals for the output multiplexers and as reference voltages for the SC line memories. Four external capacitors at the pins CLMY, CLMBY, CLMRY and BGREF respectively are necessary to provide smoothing for the reference voltages. A black level reference signal is available at CLAOUT.

#### Controller

The controller generates the clocks and the horizontal start signals for the SC line memories and, also, the control signals for the output multiplexers. The timing for the start reading signal for three different screen positions (left, centre and right) and the control signals for the multiplexers (C1 and C2) is fixed. For the uncompressed signals a bypass via the SC line memories and a bypass not via the SC line memories is available. When the signals do not pass the line memories, the frequencyresponse is not affected by the sifunction.

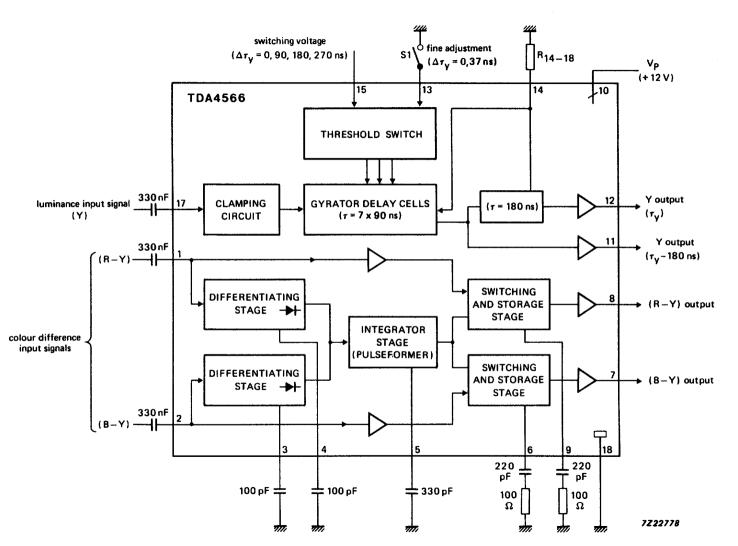

# **TDA4566**

## Colour transient improvement circuit

#### **GENERAL DESCRIPTION**

The TDA4566 is a monolithic integrated circuit for colour-transient improvement (CTI) and luminance delay line in gyrator technique in colour television receivers.

#### **Features**

- Colour transient improvement for colour difference signals (R-Y) and (B-Y) with transient detecting-, storage- and switching stages resulting in high transients of colour difference output signals

- A luminance signal path (Y) which substitutes the conventional Y-delay coil with an integrated Y-delay line

- Switchable delay time from 550 ns to 820 ns in steps of 90 ns and additional fine adjustment of 37 ns

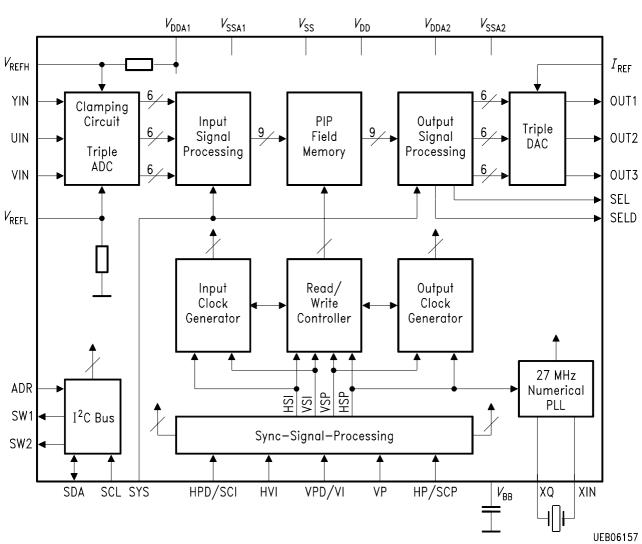

- Two Y output signals; one of 180 ns less delay

#### F19 CTI & 16:9 TO 4:3 COMPRESSOR 12 V 5 V IC2 TDA4566 **SAA4981** 15 10 THESHOLD SWT. 20 Y OUT LINE MEMORY GYRATOR **→** MUX **MUX** 8 DELAY CELLS LINE MEMORY 7 x 90 ns R-Y LINE MEMORY **OUT** MUX INTEGRATOR & PULSE B-Y LINE MEMORY **FORMER STORE** B-Y 13 **CLAMP** REFERENCE 14 11 10 H REF 5 16:9 TO 4:3 SWITCH SIGNAL **T2 DUAL MONOSTABLE** 8 V MULTIVIBRATOR c9 IC 4 HEF 4538 M.M. M.M. S.C INPUT 11 -12 V F19FEAT.DRW E.G. 12/12/99

FORMENTI

# SCANNING

# SECTION

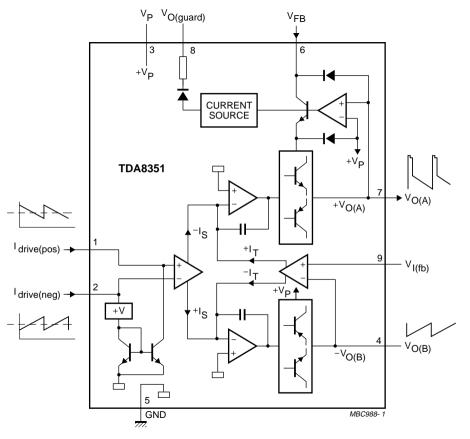

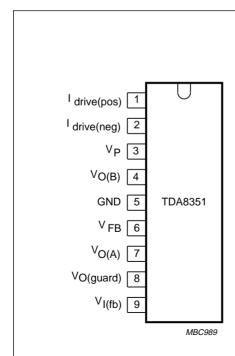

# **TDA8351**

# DC-coupled vertical deflection Circuit

#### **FEATURES**

Few external components

Highly efficient fully DC-coupled vertical output bridge circuit

Vertical flyback switch

Guard circuit

#### **Protection against:**

- short-circuit of the output pins (7 and 4)

- short-circuit of the output pins to VP

- Temperature (thermal) protection

- High EMC immunity because of common mode inputs

- A guard signal in zoom mode.

•

#### **GENERAL DESCRIPTION**

The TDA8351 is a power circuit for use in 9 and 11 colour deflection systems for field frequencies of 50 to 120 Hz. The circuit provides a DC driven vertical deflection output circuit, operating as a highly efficient class G system.

#### **FUNCTIONAL DESCRIPTION**

The vertical driver circuit is a bridge configuration. The deflection coil is connected between the output amplifiers, which are driven in phase opposition. An external resistor (RM) connected in series with the deflection coil provides internal feedback information. The differential input circuit is voltage driven. The input circuit has been adapted to enable it to be used with the TDA9150, TDA9151B, TDA9160A, TDA9162, TDA8366 and TDA8376 which deliver symmetrical current signals. An external resistor (RCON) connected between the differential input determines the output current through the deflection coil.

The relationship between the differential input current and the output current is defined by: Idiff RCON =Icoil RM.

The output current is adjustable from 0.5 A (p-p) to 3 A(p-p) by varying RM . The maximum input differential voltage is 1.8 V. In the application it is recommended that Vdiff = 1.5 V (typ). This is recommended because of the spread of input current and the spread in the value of RCON .

The flyback voltage is determined by an additional supply voltage VFB. The principle of operating with two supply voltages (class G) makes it possible to fix the supply voltage VP optimum for the scan voltage and the second supply voltage VFB optimum for the flyback voltage. Using this method, very high efficiency is achieved.

The supply voltage VFB is almost totally available as flyback voltage across the coil, this being possible due to the absence of a decoupling capacitor (not necessary, due to the bridge configuration). The output circuit is fully protected against the following: thermal protection

- short-circuit protection of the output pins (pins 4 and 7)

- short-circuit of the output pins to VP.

A guard circuit VO(guard) is provided. The guard circuit is activated at the following conditions:

- during flyback

- during short-circuit of the coil and during short-circuit of the output pins (pins 4 and 7)

to VP or ground

- during open loop

- when the thermal protection is activated. This signal can be used for blanking the picture tubescreen.

#### **PINNING**

| SYMBOL                  | PIN | DESCRIPTION                                                              |

|-------------------------|-----|--------------------------------------------------------------------------|

| I <sub>drive(pos)</sub> | 1   | input power-stage (positive);<br>includes I <sub>I(sb)</sub> signal bias |

| I <sub>drive(neg)</sub> | 2   | input power-stage (negative); includes I <sub>I(sb)</sub> signal bias    |

| V <sub>P</sub>          | 3   | operating supply voltage                                                 |

| V <sub>O(B)</sub>       | 4   | output voltage B                                                         |

| GND                     | 5   | ground                                                                   |

| $V_{FB}$                | 6   | input flyback supply voltage                                             |

| V <sub>O(A)</sub>       | 7   | output voltage A                                                         |

| V <sub>O(guard)</sub>   | 8   | guard output voltage                                                     |

| V <sub>I(fb)</sub>      | 9   | input feedback voltage                                                   |

AUDIO SECTION

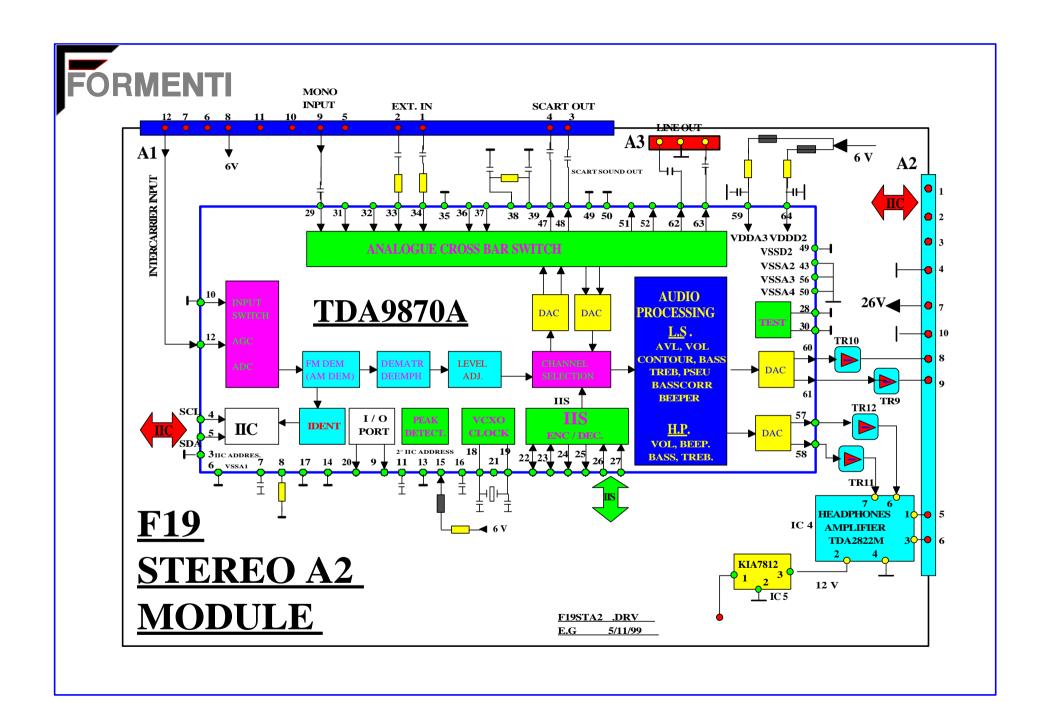

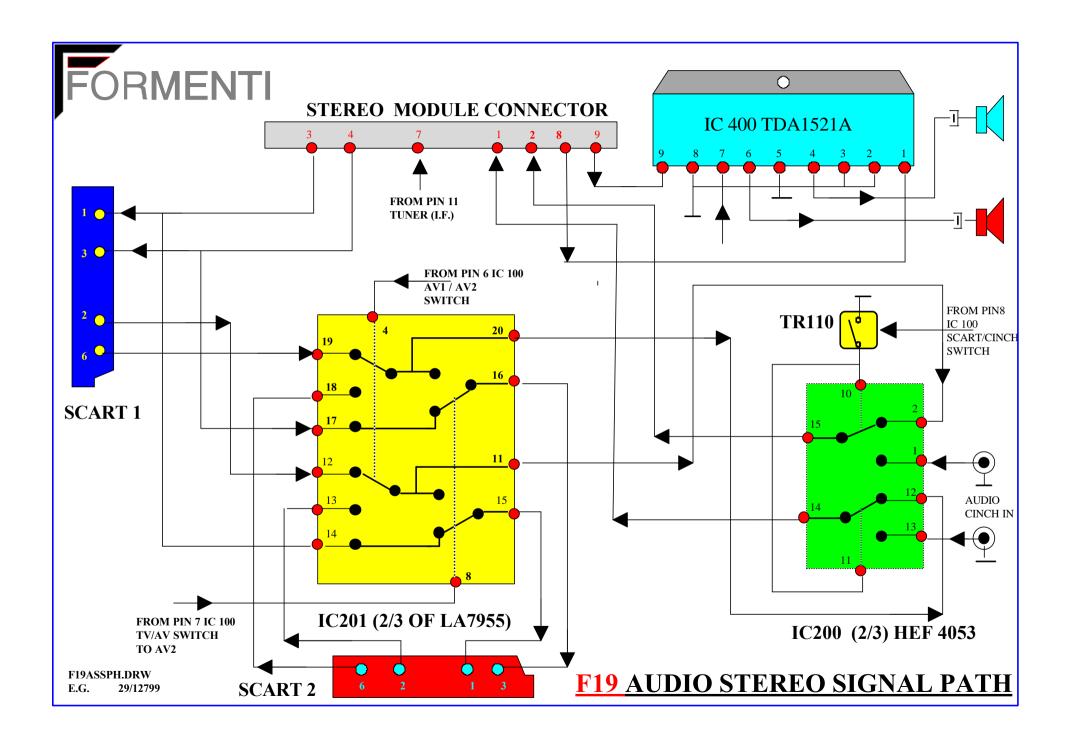

### **TDA 9870A & TDA9875A MAIN CHARACTERISTICS**

#### **FEATURES**

#### Demodulator and decoder section

- Sound IF (SIF) input switch e.g. to select between terrestrial TV SIF and SAT SIF sources SIF AGC with 24 dB control range SIF 8-bit Analog-to-Digital Converter (ADC)

- DQPSK demodulation for different standards, simultaneously with 1-channel FM demodulation NICAM decoding (B/G, I and L standard) Two-carrier multistandard FM demodulation (B/G, D/K and M standard

- Decoding for three analog multi-channel systems (A2, A2+ and A2\*) and satellite sound Optional AM demodulation for system L, simultaneously with NICAM

- Programmable identification (B/G, D/K and M standard) and different identification times.

#### • DSP section

- Digital crossbar switch for all digital signal sources and destinations

- Control of volume, balance, contour, bass, treble,

- pseudo stereo, spatial, bass boost and soft-mute

- Plop-free volume control

- Automatic Volume Level (AVL) control

- Adaptive de-emphasis for satellite

- Programmable beeper

- Monitor selection for FM/AM DC values and signals, with peak detection option

I 2 S-bus

interface for a feature extension (e.g. Dolby surround) with matrix, level adjust and

mute.

- Analog audio section

- Analog crossbar switch with inputs for mono and stereo

- (also applicable as SCART 3 input), SCART 1

- input/output, SCART 2 input/output and line output

- User defined full-level/ 3 dB scaling for SCART outputs

- Output selection of mono, stereo, dual A/B, dual A or Dual B

- 20 kHz bandwidth for SCART-to-SCART copies

- Standby mode with functionality for SCART copies

- Dual audio digital-to-analog converter from DSP to analog crossbar switch, bandwidth 15 kHz Dual audio ADC from analog inputs to DSP Two dual audio Digital-to-Analog Converters (DACs) for loudspeaker (Main) and headphone (Auxiliary) outputs; also applicable for L, R, C and S in the Dolby Pro Logic mode with feature extension.

#### **GENERAL DESCRIPTION**

The TDA9875A is a single-chip Digital TV Sound Processor (DTVSP) for analog and digital multi-channel sound systems in TV sets and satellite receivers.

#### Supported standards

The multistandard/multi-stereo capability of the TDA9875A is mainly of interest in Europe, but also in Hong Kong/Peoples Republic of China and South East Asia. This includes B/G, D/K, I, M and L standard. In other application areas there exists only subsets of those standard combinations otherwise only single standards are transmitted.

M standard is transmitted in Europe by the American Forces Network (AFN) with European channel spacing (7 MHz VHF, 8 MHz UHF) and monaural sound. The AM sound of L/L' standard is normally demodulated in the 1<sup>st</sup> sound IF. The resulting AF signal has to be entered into the mono audio input of the TDA9875A. A second possibility is to use the internal AM demodulator stage, however this gives limited performance. Korea has a stereo sound system similar to Europe and is supported by the TDA9875A. Differences include deviation, modulation contents and identification. It is based on M standard.

#### **FUNCTIONAL DESCRIPTION**

Description of the demodulator and decoder section SIF INPUT

Two input pins are provided, SIF1 e.g. for terrestrial TV and SIF2 e.g. for a satellite tuner. For higher SIF signal levels the SIF input can be attenuated with an internal switchable 10 dB resistor divider. As no specific filters are integrated, both inputs have the same specification giving flexibility in application. The selected signal is passed through an AGC circuit and then digitized by an 8-bit ADC operating at 24.576 MHz.

#### **AGC**

The gain of the AGC amplifier is controlled from the ADC output by means of a digital control loop employing hysteresis. The AGC has a fast attack behaviour to prevent ADC overloads and a slow decay behaviour to prevent AGC oscillations. For AM demodulation the AGC must be switched off. When switched off, the control loop is reset and fixed gain settings can be chosen from Table 15 (subaddress 0).

#### **MIXER**

The digitized input signal is fed to the mixers, which mix one or both input sound carriers down to zero IF. A 24-bit control word for each carrier sets the required frequency. Access to the mixer control word registers is via the I 2 C-bus. When receiving NICAM programs, a feedback signal is added to the control word of the second carrier mixer to establish a carrier-frequency loop.

#### **FM AND AM DEMODULATION**

An FM or AM input signal is fed via a band-limiting filter to a demodulator that can be used for either FM or AM demodulation. Apart from the standard (fixed) de-emphasis characteristic, an adaptive de-emphasis is available for encoded satellite programs. A stereo decoder recovers the left and right signal channels from the demodulated sound carriers. Both the European and Korean stereo systems are supported.

#### **FM IDENTIFICATION**

The identification of the FM sound mode is performed by AM synchronous demodulation of the pilot signal and narrow-band detection of the identification frequencies. The result is available via the I 2 C-bus interface. A selection can be made via the I 2 C-bus for B/G, D/K and M standard and for three different modes that represent different trade-offs between speed and reliability of identification.

#### **NICAM DEMODULATION**

The NICAM signal is transmitted in a DQPSK code at a bit rate of 728 kbit/s. The NICAM demodulator performs DQPSK demodulation and feeds the resulting bitstream and clock signal onto the NICAM decoder and, for evaluation purposes, to PCLK (pin 1) and NICAM E.G.Data creazione 01/11/99 17.27 25 / 30 F19MANU.doc

(pin 2). A timing loop controls the frequency of the crystal oscillator to lock the sampling rate to the symbol timing of the NICAM data.

#### **NICAM DECODER**

The device performs all decoding functions in accordance with the "EBU NICAM 728 specification". After locking to the frame alignment word, the data is descrambled by applying the defined pseudo-random binary sequence; the device will then synchronize to the periodic frame flag bit C0.

The status of the NICAM decoder can be read out from the NICAM status register by the user. The OSB bit indicates that the decoder has locked to the NICAM data. The VDSP bit indicates that the decoder has locked to the NICAM data and that the data is valid sound data. The C4 bit indicates that the sound conveyed by the FM mono channel is identical to the sound conveyed by the NICAM channel. The error byte contains the number of sound sample errors, resulting from parity checking, that occurred in the past 128 ms period.

#### **NICAM AUTO-MUTE**

This function is enabled by setting bit AMUTE LOW subaddress 14 Upper and lower error limits may be defined by writing appropriate values to two registers in the I 2 C-bus section (subaddresses 16 and 17; . When the number of errors in a 128 ms period exceeds the upper error limit the auto-mute function will switch the output sound from NICAM to whatever sound is on the first sound carrier (FM or AM). When the error count is smaller than the lower error limit the NICAM sound is restored. The auto-mute function can be disabled by setting bit AMUTE HIGH. In this condition clicks become audible when the error count increases; the user will hear a signal of degrading quality.

A decision to enable/disable the auto-muting is taken by the microcontroller based on an interpretation of the application control bits C1, C2, C3 and C4 and, possibly, any additional strategy implemented by the set maker in the microcontroller software.

For NICAM L applications, it is recommended to demodulate AM sound in the first sound IF and connect the audio signal to the mono input of the TDA9875A. By setting the AMSEL bit subaddress 14. the auto-mute function will switch to the audio ADC instead of switching to the first sound carrier.

#### CRYSTAL OSCILLATOR

The digital-controlled crystal oscillator (DCXO) is illustrated in Fig.8 (see Chapter 12). The circuitry of the DCXO is fully integrated, only the external 24.576 MHz crystal is needed.

#### **TEST PINS**

Both test pins are active HIGH, in normal operation of the device they are wired to VSSD1 Test functions are for manufacturing tests only and are not available to customers. Without external circuitry these pads are pulled down to LOW level with internal resistors.

#### **POWER FAIL DETECTOR**

The power fail detector monitors the internal power supply for the digital part of the device. If the supply has temporary been lower than the specified lower limit, the power-on reset bit POR, transmitter register subaddress 0 will be set to HIGH. The CLRPOR bit, slave register subaddress 1 resets the power-on reset flip-flop to LOW. If this is detected, an initialization of the TDA9875A has to be carried out to ensure reliable operation.

#### **LEVEL SCALING**

All input channels to the digital crossbar switch (except for the loudspeaker feedback path) are equipped with a level adjust facility to change the signal level in a range of 15 dB. It is recommended to scale all input channels to be 15 dB below full scale (15 dB full scale) under nominal conditions.

#### **NICAM PATH**

The NICAM path has a switchable J17 de-emphasis.

#### FM (AM) PATH

A high-pass filter suppresses DC offsets from the FM demodulator due to carrier frequency offsets and supplies the monitor/peak function with DC values and an unfiltered signal, e.g. for the purpose of carrier detection. The de-emphasis function offers fixed settings for the supported standards (50  $\mu$ s, 60  $\mu$ s 75  $\mu$ s and J17). An adaptive de-emphasis is available for Wegener-Panda 1 encoded programs. A matrix performs the dematrixing of the A2 stereo, dual and mono signals.

#### **NICAM AUTO-MUTE**

If NICAM B/G, I, D/K is received, the auto-mute is enabled and the signal quality becomes poor, the digital crossbar switch switches automatically to FM and switches the matrix to channel 1. The automatic switching depends on the NICAM bit error rate.

The auto-mute function can be disabled via the I 2 C-bus. For NICAM L applications, it is recommended to demodulate AM sound in the first sound IF and connect the audio signal to the mono input of the TDA9875A. By setting the AMSEL bit subaddress 14 (see Section 10.3.11), the auto-mute function will switch to the audio ADC instead of switching to the

first sound carrier. The ADC source selector subaddress 23 (see Section 10.3.20) should be set to mono input, where the AM sound signal should be connected.

#### LOUDSPEAKER (MAIN) CHANNEL

The matrix provides the following functions; forced mono, stereo, channel swap, channel 1, channel 2 and spatial effects.

There are fixed coefficient sets for spatial settings of 30%, 40% and 52%.

The Automatic Volume Level (AVL) function provides a constant output level of 23 dB full scale for input levels between 0 and 29 dB full scale. There are some fixed decay time constants to choose from, i.e. 2, 4 and 8 seconds.

Pseudo stereo is based on a phase shift in one channel via a 2<sup>nd</sup>-order all-pass filter. There are fixed coefficient sets to provide 90 degrees phase shift at frequencies of 150, 200 and 300 Hz.

Volume is controlled individually for each channel ranging from +24 to -83 dB with 1 dB resolution. There is also a mute position. For the purpose of a simple control software in the microcontroller, the decimal number that is sent as an I 2 C-bus data byte for volume control is identical to the volume setting in dBs (e.g. the I 2 C-bus data byte +10 sets the new volume value to +10 dB).

Balance can be realized by independent control of the left and right channel volume settings.

Contour is adjustable between 0 and +18 dB with 1 dB resolution. This function is linked to the volume setting by means of microcontroller software.

Bass is adjustable between +15 and -12 dB with 1 dB resolution and treble is adjustable between +/-12 dB with 1 dB resolution.

For the purpose of a simple control software in the microcontroller, the decimal number that is sent as an I 2 C-bus data byte for contour, bass or treble is identical to the new contour, bass or treble setting in dBs (e.g. the I 2 C-bus data byte +8 sets the new value to +8 dB). Extra bass boost is provided up to 20 dB with 2 dB resolution. The implemented coefficient set serves merely as an example on how to use this filter.

The beeper provides tones in a range from approximately 400 Hz to 30 kHz. The frequency can be selected via the I 2 C-bus. The beeper output signal is added to the the loudspeaker and headphone channel signals. The beeper volume is adjustable with

respect to full scale between 0 and 93 dB with 3 dB resolution. The beeper is not effected by mute.

Soft-mute provides a mute ability in addition to volume control with a well defined time (32 ms) after which the soft-mute is completed. A smooth fading is achieved by a cosine masking.

#### **HEADPHONE (AUXILIARY) CHANNEL**

The matrix provides the following functions; forced mono, stereo, channel swap, channel and channel 2 (or C and S in Dolby Surround Pro Logic mode). Volume is controlled individually for each channel in a range from +24 to 83 dB with 1 dB resolution. There is also a mute position. For the purpose of a simple control software in the microcontroller, the decimal number that is sent as an I 2 C-bus data byte for volume control is identical to the volume setting in dB (e.g. the I 2 C-bus data byte +10 sets the new volume value to +10 dB). Balance can be realized by independent control of the left and right channel volume settings.

Bass is adjustable between +15 and -12 dB with 1 dB resolution and treble is adjustable between +/- 12 dB with 1 dB resolution.

For the purpose of a simple control software in the microcontroller, the decimal number that is sent as an I 2 C-bus data byte for bass or treble is identical to the new bass or treble setting in dB (e.g. the I 2 C-bus data byte +8 sets the new value to +8 dB).

The beeper provides tones in a range from approximately 400 Hz to 30 kHz. The frequency can be selected via the I 2 C-bus. The beeper output signal is added to the loudspeaker and headphone channel signals. The beeper volume is adjustable with respect to full scale between 0 and 93 dB with 3 dB resolution. The beeper is not effected by mute.

Soft-mute provides a mute ability in addition to volume control with a well defined time (32 ms) after which the soft-mute is completed. A smooth fading is achieved by a cosine masking.

#### **SCART INPUTS**

The SCART specification allows for a signal level of up to 2 V (rms). Because of signal handling limitations, due to the 5 V supply voltage of the TDA9875A, it is necessary to have fixed 3 dB attenuators at the SCART inputs to obtain a 2 V input. This results in a +3 dB SCART-to-SCART copy gain. If 0 dB copy gain is preferred (with maximum 1.4V input), there are +3 dB/0 dB amplifiers at the outputs of SCART 1 and SCART 2 and at the line E.G.Data creazione 01/11/99 17.27 29 / 30 F19MANU.doc

output. The input attenuator is realized by an external series resistor in combination with the input impedance, both of which form a voltage divider. With this voltage divider the maximum SCART signal level of 2 V (rms) is scaled down to 1.4 V (rms) at the input pin.

#### **EXTERNAL AND MONO INPUTS**

The 3 dB input attenuators are not required for the external and mono inputs, because those signal levels are under control of the TV designer. The maximum allowed input level is 1.4 V (rms). By adding external series resistors, the external inputs can be used as an additional SCART input.

#### **SCART OUTPUTS**

The SCART outputs employ amplifiers with two gain settings. The gain can be set to +3 dB or to 0 dB via the I 2 C-bus. The +3 dB position is needed to compensate for the 3 dB attenuation at the SCART inputs should SCART-to-SCART copies with 0 dB gain be preferred [under the condition of 1.4 V (rms) maximum input level]. The 0 dB position is needed, for example, for an external-to-SCART copy with 0 dB gain.

#### **LINE OUTPUT**

The line output can provide an unprocessed copy of the audio signal in the loudspeaker channels. This can be either an external signal that comes from the dual audio ADC, or a signal from an internal digital audio source that comes from the dual audio DAC. The line output employs amplifiers with two gain settings. The +3 dB position is needed to compensate for the attenuation at the SCART inputs, while the 0 dB position is needed, for example, for non-attenuated external or internal digital signals (see Section 6.3.4).

## **TDA9811**

# Multistandard VIF-PLL with QSS-IF and AM demodulator

#### **FEATURES**

- 5 V supply voltage

- Two switched VIF inputs, gain controlled wide band VIF-amplifier (AC-coupled)

- True synchronous demodulation with active carrier regeneration (very linear demodulation, good intermodulation figures, reduced harmonics, excellent pulse response)

- Gated phase detector for L/L accent standard VCO frequency switchable between L and L accent (alignment external) picture carrier frequency

- Separate video amplifier for sound trap buffering with high video bandwidth VIF AGC detector for gain control, operating as peak sync detector for B/G (optional external AGC) and peak white detector for L; signal controlled reaction time for L

- Tuner AGC with adjustable takeover point (TOP)

- AFC detector without extra reference circuit

- SIF input for single reference QSS mode (PLL controlled); SIF AGC detector for gain controlled SIF amplifier; single reference QSS mixer able to operate in high performance single reference QSS mode

- AM demodulator without extra reference circuit

- AM mute (especially for NICAM)

- Stabilizer circuit for ripple rejection and to achieve constant output signals.

#### **GENERAL DESCRIPTION**

The TDA9811 is an integrated circuit for multistandard vision IF signal processing and sound AM demodulation, with single reference QSS-IF in TV and VCR sets.

TDA9811 QSS Pagina 1 di 4 e.g. TDA9811R

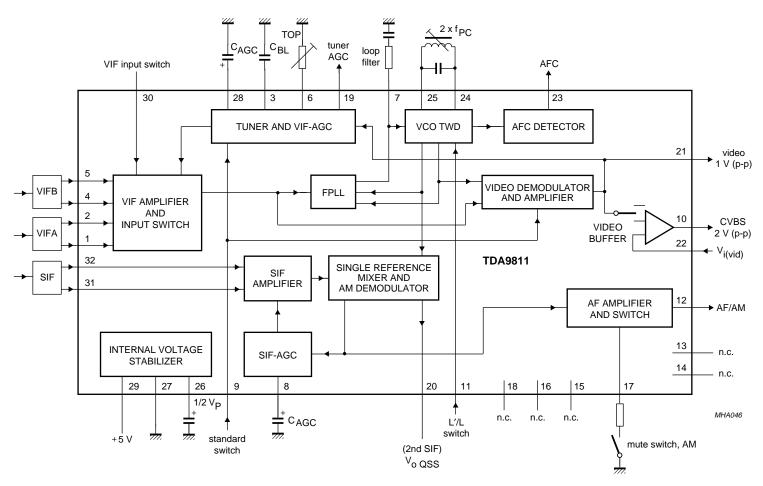

#### **FUNCTIONAL DESCRIPTION**

Vision IF amplifier and input switch The vision IF amplifier consists of three AC-coupled differential amplifier stages. Each differential stage comprises a feedback network controlled by emitterdegeneration. T

The first differential stage is extended by two pairs of emitter followers to provide two IF input channels. The VIF input can be selected by pin 30

#### **Tuner and VIF AGC**

The AGC capacitor voltage is transferred to an internal IF control signal, and is fed to the tuner AGC to generate the tuner AGC output current (open-collector output).

The tuner AGC takeover point can be adjusted. This allows the tuner and the SWIF filter to be matched to achieve the optimum IF input level.

The AGC detector charges/discharges the AGC capacitor to the required voltage for setting of VIF and tuner gain in order to keep the video signal at a constant level.

Therefore for negative video modulation the sync level and for positive video modulation the peak white level of the video signal is detected. In order to reduce the reaction time for positive modulation, where a very large time constant is needed, an additional level detector increases the discharging current of the AGC capacitor (fast mode) in the event of a decreasing VIF amplitude step. The additional level information is given by the black-level detector voltage.

#### Frequency Phase Locked Loop detector (FPLL)

The VIF-amplifier output signal is fed into a frequency detector and into a phase detector via a limiting amplifier.

During acquisition the frequency detector produces a DC current proportional to the frequency difference between the input and the VCO signal. After frequency lock-in the phase detector produces a DC current proportional to the phase difference between the VCO and the input signal. The DC current of either frequency detector or phase detector is converted into a DC voltage via the loop filter, which controls the VCO frequency. In the event of positive modulated signals the phase detector is gated by composite sync in order to avoid signal distortion for overmodulated VIF signals.

#### VCO, Travelling Wave Divider (TWD) and AFC

The VCO operates with a resonance circuit (with L and C in parallel) at double the PC frequency. The VCO is controlled by two integrated variable capacitors.

The control voltage required to tune the VCO from its free-running frequency to actually double the PC frequency is generated by the frequency-phase detector and fed via the loop filter to the first variable capacitor (FPLL). This control voltage is amplified and additionally converted into a current which represents the AFC output signal. The VCO centre frequency can be decreased (required for L accent standard) by activating an additional internal capacitor. This is achieved by using the L accent switch. In this event the second variable capacitor can be controlled by a variable resistor at the L accent switch for setting the VCO centre frequency to the required L accent value. At centre frequency the AFC output current is equal to zero.

The oscillator signal is divided-by-two with a TWD which generates two differential output signals with a 90 degree phase difference independent of the frequency.

#### Video demodulator and amplifier

The video demodulator is realized by a multiplier which is designed for low distortion and large bandwidth. The vision IF input signal is multiplied with the 'in phase' signal of the travelling wave divider output. In the demodulator stage the video signal polarity can be switched in accordancewith the TV standard. The demodulator output signal is fed via an integrated low-pass filter for attenuation of the carrier harmonics to the video amplifier. The video amplifier is realized by an operational amplifier with internal feedback and high bandwidth. A low-pass filter is integrated to achieve an attenuation of the carrier harmonics for B/G and L standard. The standard dependent level shift in this stage delivers the same sync level for positive and negative modulation. The video output signal is 1 V (p-p) for nominal vision IF modulation.

#### Video buffer

For an easy adaption of the sound traps an operational amplifier with internal feedback is used in the event of B/G and L standard. This amplifier is featured with a high bandwidth and 7 dB gain. The input impedance is adapted output stage delivers a nominal 2 V (p-p) positive video signal. Noise clipping is provided.

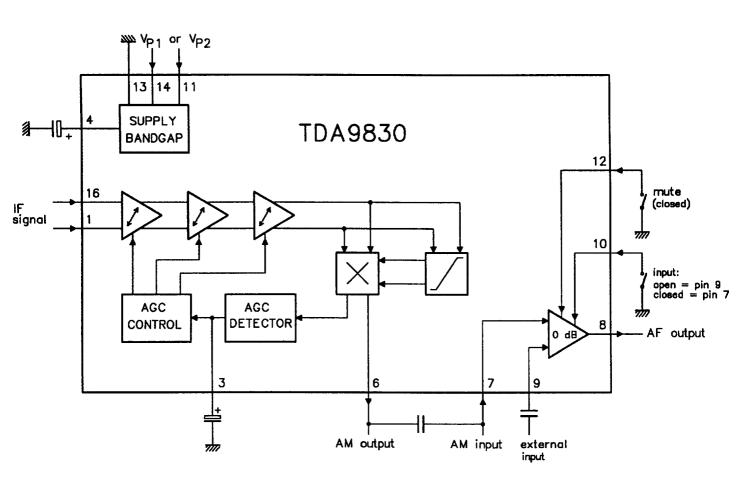

#### SIF amplifier and AGC

The sound IF amplifier consists of two AC-coupled differential amplifier stages. Each differential stage comprises a controlled feedback network provided by emitter degeneration. The SIF AGC detector is related to the SIF input signals (average level of AM or FM carriers) and controls the SIF amplifier to provide a constant SIF signal to the AM demodulator and single reference QSS mixer. The SIF AGC reaction time is set to 'slow' for nominal video conditions. But with a decreasing VIF amplitude step the SIF AGC is set to 'fast' mode controlled by the VIF AGC detector. In FM mode this reaction time is also set to 'fast' controlled by the standard switch.

**Single reference QSS mixer** The single reference QSS mixer is realized by a multiplier.

The SIF amplifier output signal is fed to the single reference QSS mixer and converted to intercarrier frequency by the regenerated picture carrier (VCO).

The mixer output signal is fed via a high-pass for attenuation of the video signal components to the output pin 20. With this system a high performance hi-fi stereo sound processing can be achieved.

#### AM demodulator

The AM demodulator is realized by a multiplier. The modulated SIF amplifier output signal is multiplied in phase with the limited (AM is removed) SIF amplifier output signal. The demodulator output signal is fed via an integrated low-pass filter for attenuation of the carrier harmonics to the AF amplifier.

#### Internal voltage stabilizer and 1 ¤2 VP -reference

The bandgap circuit internally generates a voltage of approximately 1.25 V, independent of supply voltage and temperature. A voltage regulator circuit, connected to this voltage, produces a constant voltage of 3.6 V which is used as an internal reference voltage.

For all audio output signals the constant reference voltage cannot be used because large output signals are required.

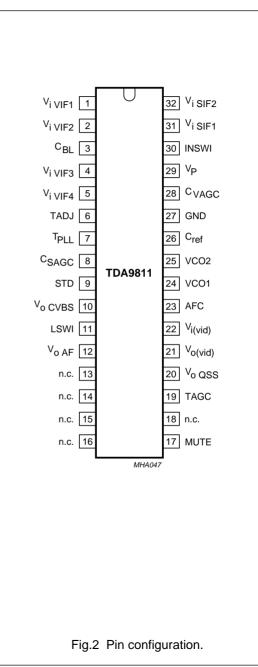

#### **PINNING**

| SYMBOL              | PIN | DESCRIPTION                                 |  |

|---------------------|-----|---------------------------------------------|--|

| V <sub>i VIF1</sub> | 1   | VIF differential input signal voltage 1     |  |

| V <sub>i VIF2</sub> | 2   | VIF differential input signal voltage 2     |  |

| C <sub>BL</sub>     | 3   | black level detector                        |  |

| V <sub>i VIF3</sub> | 4   | VIF differential input signal voltage 3     |  |

| V <sub>i VIF4</sub> | 5   | VIF differential input signal voltage 4     |  |

| TADJ                | 6   | tuner AGC takeover adjust (TOP)             |  |

| T <sub>PLL</sub>    | 7   | PLL loop filter                             |  |

| C <sub>SAGC</sub>   | 8   | SIF AGC capacitor                           |  |

| STD                 | 9   | standard switch                             |  |

| V <sub>o CVBS</sub> | 10  | CVBS output signal voltage                  |  |

| LSWI                | 11  | L/L accent switch                           |  |

| V <sub>o AF</sub>   | 12  | AM audio voltage frequency output           |  |

| n.c.                | 13  | not connected                               |  |

| n.c.                | 14  | not connected                               |  |

| n.c.                | 15  | not connected                               |  |

| n.c.                | 16  | not connected                               |  |

| MUTE                | 17  | AM mute                                     |  |

| n.c.                | 18  | not connected                               |  |

| TAGC                | 19  | tuner AGC output                            |  |

| V <sub>o QSS</sub>  | 20  | single reference QSS output voltage         |  |

| V <sub>o(vid)</sub> | 21  | composite video output voltage              |  |